CAN可靠性

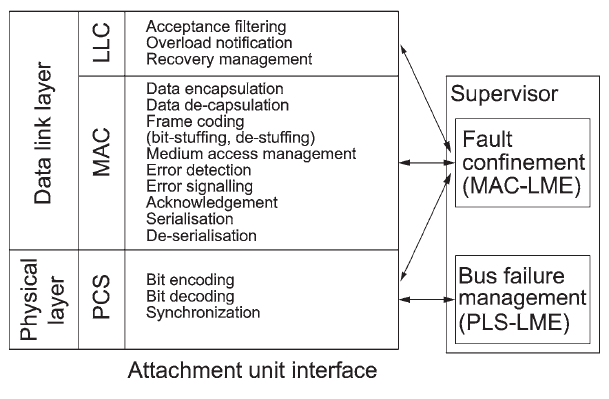

CAN物理層收發器的一個重大性能革命在于它實現了自身抵御系統噪聲的干擾,無論有無外部的保護器件。在定義CAN物理層時需要考慮多種規范的需求。

為了解決這些挑戰,在 (EME、EMI、ESD) 領域,利用先進的混合信號和電源技術SMARTMOS 8工藝,已經開發出一系列豐富多樣的創新,以便實現系統可靠性的提升,并且無需外部扼流圈保護便可達到標準。

抗干擾設計:

CAN網絡如同吸收電磁噪聲的天線,它通過類似電動機、電磁閥、繼電器這樣負載切換或者通過外部來源生成。在CAN通信期間,當施加電磁噪聲時,信號完整性不能被干擾。

這被稱為電磁抗干擾(EMI)。主要采用兩種EMI測試模擬以驗證物理層的可靠性:分別是直接功率注入法(IEC62132-4)和大電流注入法(ISO11452-4) [2]。

在外部EMC的入侵下,MCU TxD和RxD終端之間數據的傳輸和接收的信號應該在一定范圍內震蕩。隨著傳輸速率的提高,數據的保持時間會減少,所能接受的信號震蕩容限范圍會隨之降低這需要CAN收發器具備出色的EMC性能。

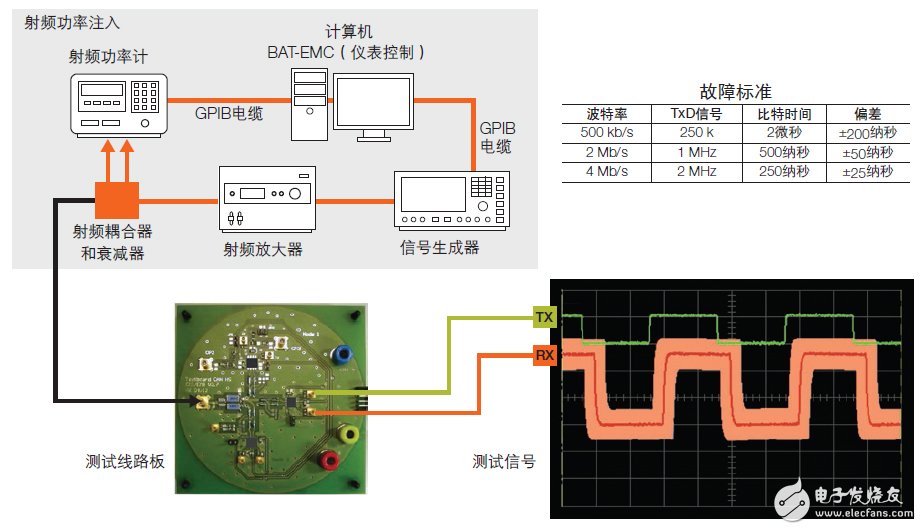

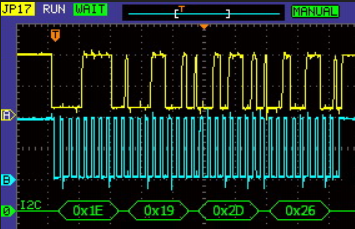

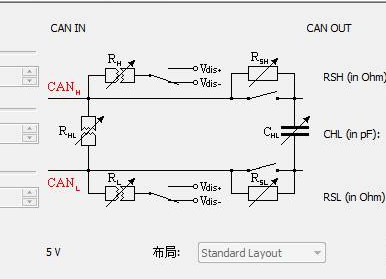

下圖為EMC測試原理的簡化圖,通過耦合電容器施加射頻干擾,同時收發器向總線傳輸數據。監控收發器RxD信號,并與信號模板對比,它包含了允許的電壓和時序偏差(抖動)的典型信號。這種波動會變得越來越小,以適應CAN FD的運行。

EMC測試設置和容差范圍簡化示意圖

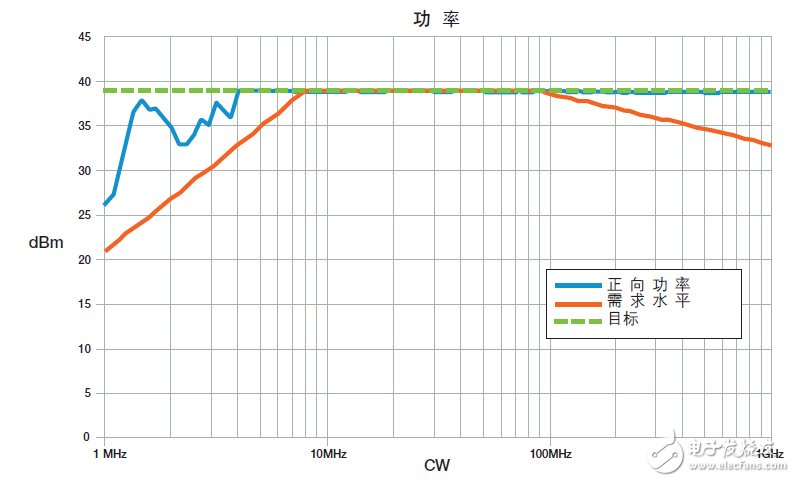

在物理層中,可以提供完整的EMC設計流程,包括準確的設計和布局指南、豐富的模塊級和頂層單元級仿真以及EMC仿真內部運行中包括了工藝和溫度變量在內的各種模型,從而針對技術規范確保一定程度內的余量。由此,這些設計的改進確保了CAN信號完整性,支持信號注入量達到39 dBm。

通過CAN FD使用案例,不受EMC的限制,部分傳播延遲還可以經過優化,從而實現更高波特率的運行。這種物理層設計的演變對抗干擾性產生了影響,允許的抖動窗口變得越來越小。噪聲敏感度也因此增強,設計需要更高的抗干擾解決方案。下圖展示了在2 Mb/s的使用案例情況下,飛思卡爾MC33901 CAN高速物理層通過了DPI注入的性能。

MC33901/MC34901 – 帶有扼流圈時的直接功率注入CAN,2 Mb/s

憑借高ESD性能提高系統可靠性:

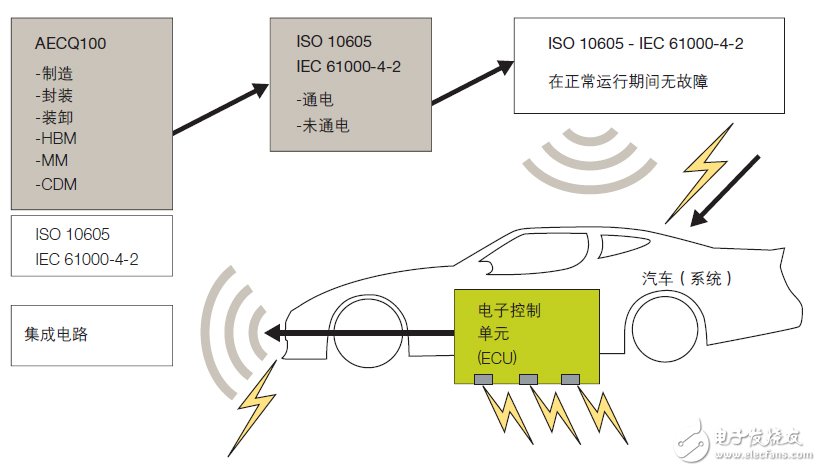

物理層有專門的設計用于承受IC級和系統級定義的最嚴格ESD標準。它通過了AEC Q-100文檔中的規定ESD測試:人體模型(HBM) +-10 kV、機器模型(MM) +-200 V和帶電設備模型(CDM) +-750 V。此外,物理層經過優化,還通過了ISO10605:2008 [3]、IEC61000-4-2:2008 [4]、HMM(人人體金屬模型)[5]定義的系統級壓力測試。

ESD GUN可以用于重現人體處理電子系統子部件或者接觸汽車/設備結構時靜電放電的影響。測試物理層所用的標準為ISO10605:2008、EN 61000-4-2:2008技術規范,IC上電和未上電。在集成電路開發階段必須考慮到所有這些標準,因為每一種標準的設置變量都會導致不同的抗壓特性。

系統級到組件級的ESD技術規范

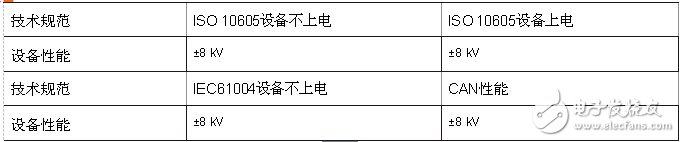

CAN H和CAN L引腳具有強大的抗靜電電壓等級,可以預防直接施加在引腳級的系統級壓力,無論帶或不帶外部保護。為了獲得這樣的高性能(25 kV),采用了SEED [7]方法(系統高效ESD設計推廣一種板載和片上芯片ESD保護的IC/OEM協同設計方法,從而獲得系統級ESD)。下表歸納了一個飛思卡爾CAN高速物理層的ESD性能實例。

ESD性能匯總

高ESD和DPI的性能組合是對能量吸收的挑戰,同時不可降低CAN通信速度。如上表所示,最新的CAN物理層旨在通過所有組件和系統ESD壓力測試,同時對外部EMI干擾免疫,無論是否添加外部組件(例如扼流圈),并且處于最優的裸片區域內。所有這些創新構成物理層進一步集成(系統基礎芯片(SBC)、ASSP、ASIC)的可靠性的基礎。這些限制條件相互組合,是IC架構的基礎所在,從而成功通過最終驗收。

本文選自電子發燒友網7月《汽車電子特刊》Change The World欄目,轉載請注明出處!

用戶評論(0)