在亞微米以下的電路設(shè)計(jì)中,需要對(duì)電路進(jìn)行全芯片的ESD保護(hù)結(jié)構(gòu)的設(shè)計(jì)。如何使全芯片有效面積盡可能小、ESD性能可靠性滿足要求且不需要增加額外的工藝步驟成為全芯片設(shè)計(jì)者的主

2012-04-23 10:17:42 3374

3374

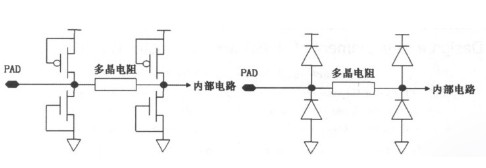

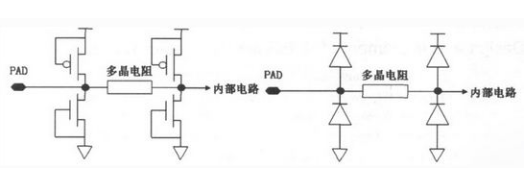

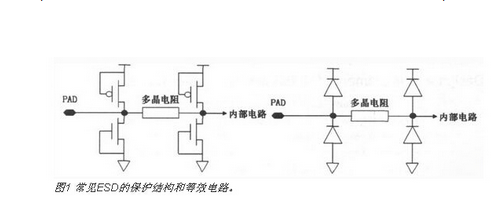

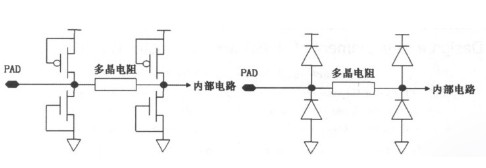

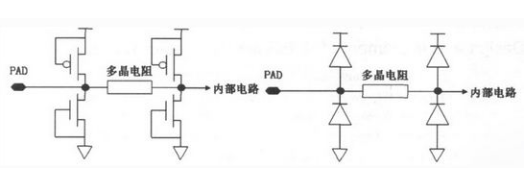

大部分的ESD電流來(lái)自電路外部,因此ESD保護(hù)電路一般設(shè)計(jì)在PAD旁,I/O電路內(nèi)部。典型的I/O電路由輸出驅(qū)動(dòng)和輸入接收器兩部分組成。ESD 通過(guò)PAD導(dǎo)入芯片內(nèi)部,因此I/O里所有與PAD直接

2014-12-24 11:05:47 2546

2546

要求,重點(diǎn)討論了在I/O電路中ESD保護(hù)結(jié)構(gòu)的設(shè)計(jì)要求。 1 引言 靜電放電會(huì)給電子器件帶來(lái)破壞性的后果,它是造成集成電路失效的主要原因之一。隨著集成電路工藝不斷發(fā)展,CMOS電路的特征尺寸不斷縮小,管子的柵氧厚度越來(lái)越薄,芯片的面積規(guī)模越來(lái)越大,MOS管能

2017-12-05 09:03:40 12076

12076

近年來(lái),有關(guān)將CMOS工藝在射頻(RF)技術(shù)中應(yīng)用的可能性的研究大量增多。深亞微米技術(shù)允許CMOS電路的工作頻率超過(guò)1GHz,這無(wú)疑推動(dòng)了集成CMOS射頻電路的發(fā)展。目前,幾個(gè)研究組已利用標(biāo)準(zhǔn)

2021-07-29 07:00:00

, EOS等各項(xiàng)指標(biāo)的要求。隨著IC先進(jìn)制程技術(shù)的應(yīng)用, 芯片功能的增多和尺寸的減小, 對(duì)于半導(dǎo)體廠和設(shè)計(jì)公司來(lái)說(shuō), 不斷面臨著產(chǎn)品對(duì)靜電保護(hù)ESD提出的越來(lái)越高的要求。這次授課老師為Bart Keppens

2015-04-22 22:19:54

。 IC制造商已經(jīng)將ESD損傷確定為互補(bǔ)式金屬氧化物半導(dǎo)體(CMOS)元件現(xiàn)場(chǎng)可靠性的一項(xiàng)主要威脅,它可能損害品牌形象并妨礙市場(chǎng)接受新技術(shù)。為避免此情況,業(yè)界積極努力用后續(xù)新制程世代來(lái)最佳化整合ESD

2011-11-24 15:00:58

統(tǒng)提供ESD保護(hù),可以從不同的角度來(lái)著手。一種方法是在半導(dǎo)體芯片內(nèi)建ESD保護(hù)架構(gòu)。不過(guò),日趨縮小的CMOS芯片已經(jīng)越來(lái)越不足以承受進(jìn)行內(nèi)部2kV等級(jí)的ESD保護(hù)所需要的面積。安森美半導(dǎo)體標(biāo)準(zhǔn)產(chǎn)品部

2008-07-29 09:51:53

UM5051/5052的重要參數(shù)ESD保護(hù)器件的種類ESD應(yīng)用舉例

2021-04-02 07:37:30

能夠承受ESD的沖擊,并繼續(xù)正常工作。ESD保護(hù)方法為了給電子系統(tǒng)提供ESD保護(hù),可以從不同的角度來(lái)著手。一種方法是在半導(dǎo)體芯片內(nèi)建ESD保護(hù)架構(gòu)。不過(guò),日趨縮小的CMOS芯片已經(jīng)越來(lái)越不足以承受進(jìn)行

2011-07-05 14:19:03

取舍,實(shí)際上會(huì)使系統(tǒng)整體性能在某種程度上受損。對(duì)于設(shè)計(jì)能夠同時(shí)符合更高數(shù)據(jù)率和更好ESD保護(hù)新需求的芯片的制造商來(lái)說(shuō),要實(shí)現(xiàn)這個(gè)目標(biāo)極具挑戰(zhàn)性。ESD保護(hù)領(lǐng)域的變化 由于采用更小的制造幾何尺寸、片上保護(hù)

2011-01-27 10:35:10

水平,以便使那些采用了對(duì)ESD越來(lái)越敏感的IC的終端產(chǎn)品保持高可靠性。 ESD波形 以系統(tǒng)級(jí)的方法來(lái)定義典型的ESD事件所采用的最常見(jiàn)的波形,是以其亞納秒上升時(shí)間和高電流電平(參見(jiàn)圖1)為顯著特征

2010-08-18 19:44:07

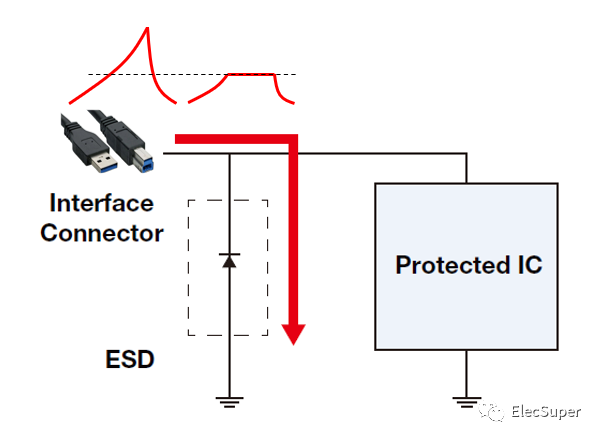

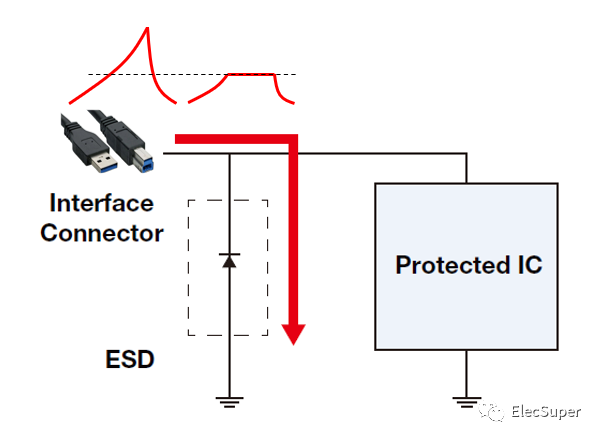

徑,把異常電壓箝制在一個(gè)安全的水平,從而保護(hù)被保護(hù)IC或線路。ESD二極管憑借體積小、封裝多樣化、響應(yīng)速度快(小于1ns)、電容值低、漏電流低(小于1uA)、超低箝位電壓、電壓值低等獨(dú)有優(yōu)勢(shì),廣泛應(yīng)用

2018-10-17 16:04:52

如何正確保護(hù)IC?ESD傳遞模式有哪幾種?ESD保護(hù)和應(yīng)用電路如何提高ESD保護(hù)?

2021-04-23 06:23:47

ESD波形是什么ESD方面所需考慮因素ESD如何選擇最有效的保護(hù)方案

2021-04-08 06:07:41

告訴《中國(guó)電子報(bào)》記者,據(jù)統(tǒng)計(jì),超過(guò)60%的IC失效都源于ESD。 隨著超大規(guī)模集成電路工藝的高速發(fā)展,特征尺寸已經(jīng)到深亞微米階段,大大提高了集成電路的性能及運(yùn)算速度,但隨著器件尺寸的減小,對(duì)可靠性

2013-02-21 10:54:18

對(duì)電子器件來(lái)說(shuō),一次我們無(wú)法察覺(jué)的輕微靜電放電就可能對(duì)其造成嚴(yán)重的損傷。泰科電子瑞侃電路保護(hù)產(chǎn)品應(yīng)用工程經(jīng)理董告訴《中國(guó)電子報(bào)》記者,據(jù)統(tǒng)計(jì),超過(guò)60%的IC失效都源于ESD。 隨著

2013-08-16 10:22:02

[table][tr][td]隨著現(xiàn)代社會(huì)的飛速發(fā)展,我們對(duì)電子設(shè)備的依靠與日俱增.現(xiàn)代電腦越來(lái)越多的采用低功率邏輯芯片,由于MOS的電介質(zhì)擊穿和雙極反向結(jié)電流的限制,使這些邏輯芯片對(duì)ESD非常敏感

2013-11-20 15:43:19

`隨著半導(dǎo)體工藝尺寸從微米量級(jí)向納米量級(jí)縮小,靜電放電(ESD)對(duì)于半導(dǎo)體器件與系統(tǒng)的影響仍在持續(xù)。本書從全芯片ESD設(shè)計(jì)綜合的角度,對(duì)EOS、ESD以及Latchup進(jìn)行了探討。針對(duì)ESD保護(hù)

2013-09-04 09:17:26

因?yàn)橐蟾呒啥取⒖焖俣群托◇w積,如今的新興電子產(chǎn)品都使用基于先進(jìn)深次微米制程的芯片。但制程越先進(jìn),芯片對(duì) ESD 耐受度也就越差。當(dāng)這些電子產(chǎn)品在實(shí)際環(huán)境下受到 ESD沖擊時(shí),IC 內(nèi)部更容易受到

2013-06-14 16:42:50

(螺絲起子)靠近有相反電勢(shì)的集成電路(IC)時(shí),電荷“跨接”,引起靜電放電(ESD)。 ESD以極高的強(qiáng)度很迅速地發(fā)生,通常將產(chǎn)生足夠的熱量熔化半導(dǎo)體芯片的內(nèi)部電路,在電子顯微鏡下外表象向外吹出的小?彈孔

2018-10-11 16:10:23

PCB和系統(tǒng)級(jí)設(shè)計(jì)中的EMI控制。在考慮EMI控制時(shí),設(shè)計(jì)工程師及PCB板級(jí)設(shè)計(jì)工程師首先應(yīng)該考慮IC芯片的選擇。集成電路的某些特征如封裝類型、偏置電壓和芯片的:工藝技術(shù)(例如CMoS、ECI)等都對(duì)電磁干擾有很大的影響。下面將著重探討IC對(duì)EMI控制的影響。

2019-05-31 07:28:26

、丟失等,必將造成巨大的損失。所以IC卡芯片對(duì)ESD有較高的要求,一般大于4kV。 防護(hù)ESD的一種有效方法,即設(shè)計(jì)特定的保護(hù)電路。圖4即為一種基于CMOS工藝的IC卡芯片ESD保護(hù)電路7。該結(jié)構(gòu)包括

2018-11-05 15:57:30

analysis、故障覆蓋率分析、測(cè)試矢量生成等目的。現(xiàn)代VLSI特別是ULSI IC的迅速發(fā)展, 正是依靠EDA工具在亞微米和深亞微米技術(shù)上的進(jìn)步及其對(duì)應(yīng)工藝水平的提高。應(yīng)該說(shuō)沒(méi)有EDA工具就沒(méi)有

2011-12-19 16:50:52

。不過(guò),日趨縮小的CMOS芯片已經(jīng)越來(lái)越不足以承受進(jìn)行內(nèi)部2 kV等級(jí)的ESD保護(hù)所需要的面積。安森美半導(dǎo)體標(biāo)準(zhǔn)產(chǎn)品部亞太區(qū)市場(chǎng)營(yíng)銷副總裁麥滿權(quán)指出:真正有效的ESD保護(hù)是不能完全集成到CMOS芯片之中

2013-01-04 14:58:24

為了給電子系統(tǒng)提供ESD保護(hù),可以從不同的角度來(lái)著手。一種方法是在半導(dǎo)體芯片內(nèi)建ESD保護(hù)架構(gòu)。不過(guò),日趨縮小的CMOS芯片已經(jīng)越來(lái)越不足以承受進(jìn)行內(nèi)部2KV等級(jí)的ESD保護(hù)所需要的面積。真正有效

2014-02-14 10:30:16

HAL250低功耗霍爾開(kāi)關(guān)是采?BCD工藝制作的全極低功耗霍爾ic,BCD?藝把雙極?藝和CMOS工藝,DMOS工藝同時(shí)制作在同一芯?上。HAL250低功耗霍爾開(kāi)關(guān)綜合了雙極器件高耐壓、強(qiáng)負(fù)載的驅(qū)動(dòng)

2021-10-14 11:45:24

的猖獗,給這個(gè)行業(yè)帶來(lái)了許多問(wèn)題,中國(guó)電子行業(yè)起步晚,發(fā)展快,但是在部分領(lǐng)域與國(guó)外技術(shù)還是存在一定的差距,尤其是智能手機(jī)芯片技術(shù)上面更是差距最大,而芯片解密技術(shù)尤其瘋狂,所有現(xiàn)在芯片加密將保護(hù)知識(shí)產(chǎn)權(quán)

2013-09-23 11:29:13

的安全保護(hù)傘的所有部分都應(yīng)該“硬化”或者屏蔽攻擊,包括加密密鑰、驗(yàn)證碼和固件。深聯(lián)華 基于硬件的安全性可在很小的空間內(nèi)通過(guò)簡(jiǎn)單且高成本效益的方式實(shí)現(xiàn)這一目標(biāo)。幾乎沒(méi)有任何方法可以下載已鎖定在芯片中的秘密

2013-12-30 16:04:47

充放電模式測(cè)試(CDM),JS002 ;閂鎖測(cè)試(LU),JESD78 ;芯片IC失效分析 ( FA):光學(xué)檢查(VI/OM) ;掃描電鏡檢查(FIB/SEM)微光分析定位(EMMI/InGaAs

2020-05-17 20:50:12

摘 要:EDA技術(shù)是現(xiàn)代電子設(shè)計(jì)技術(shù)的核心,它在現(xiàn)代集成電路設(shè)計(jì)中占據(jù)重要地位。隨著深亞微米與超深亞微米技術(shù)的迅速發(fā)展,F(xiàn)PGA設(shè)計(jì)越來(lái)越多地采用基于VHDL的設(shè)計(jì)方法及先進(jìn)的EDA工具。本文詳細(xì)

2019-06-18 07:33:04

摘 要:EDA技術(shù)是現(xiàn)代電子設(shè)計(jì)技術(shù)的核心,它在現(xiàn)代集成電路設(shè)計(jì)中占據(jù)重要地位。隨著深亞微米與超深亞微米技術(shù)的迅速發(fā)展,F(xiàn)PGA設(shè)計(jì)越來(lái)越多地采用基于VHDL的設(shè)計(jì)方法及先進(jìn)的EDA工具。本文詳細(xì)

2019-06-27 08:01:28

HDMI接收器和發(fā)射器的IC芯片全部采用深亞微米工藝制造。亞微米CMOS制程十分敏感,通常設(shè)有ESD保護(hù)限制(最高2kV),必須符合人體放電模式(HBM)標(biāo)準(zhǔn)。另外,LCD電視和機(jī)頂盒(STB)等

2013-11-21 09:57:59

和發(fā)射器IC芯片采用的是亞微米CMOS工藝制造而成的,而亞微米CMOS十分地敏感,為此需要借助ESD靜電保護(hù)器件和ESD靜電保護(hù)解決方案為其保駕護(hù)航。機(jī)頂盒STB、電視LCD等終端應(yīng)用極其容易受到ESD

2020-12-31 15:57:17

已經(jīng)過(guò)第三方實(shí)驗(yàn)室驗(yàn)證。 產(chǎn)品特點(diǎn)及其優(yōu)點(diǎn)l CMOS霍爾IC技術(shù)l 強(qiáng)大的抗RF噪聲技術(shù)l 工作電壓1.8至6V,適用于電池供電的應(yīng)用l 低至1.65V的工作電壓,全極霍爾開(kāi)關(guān)微功耗l 高靈敏度可替換

2019-11-07 10:34:36

)的沖擊經(jīng)由NFC天線對(duì)整個(gè)NFC的溝通功能所造成的錯(cuò)誤動(dòng)作。移動(dòng)電話這些電子產(chǎn)品由于頻繁地與人體接觸,很容易受到靜電放電(ESD)的沖擊。此外,這些電子產(chǎn)品所采用的IC大多是使用最先進(jìn)的半導(dǎo)體制程技術(shù),所

2019-06-13 08:18:01

TVS的ESD保護(hù)原理ESD TVS器件采用的技術(shù)匯總

2021-04-02 06:19:56

的應(yīng)用很容易受到靜電放電的影響。一些采用了深亞微米工藝和甚精細(xì)線寬布線的復(fù)雜半導(dǎo)體功能電路,對(duì)電路瞬變過(guò)程的影響更加敏感,將導(dǎo)致上述的問(wèn)題更加激化。電路保護(hù)元件存在幾種技術(shù),當(dāng)選擇電路保護(hù)元件時(shí),若

2019-07-29 17:50:09

的電路板空間以及被保護(hù)電路的電特性來(lái)決定。因?yàn)槔孟冗M(jìn)工藝技術(shù)**的IC電路里氧化層比較薄,柵極氧化層更易受到損害。而且一些采用深亞微米工藝和甚精細(xì)線寬布線的復(fù)雜半導(dǎo)體功能電路,對(duì)電路瞬變過(guò)程的影響更加

2018-11-20 14:09:05

如今的電子系統(tǒng)中越來(lái)越多地采用以CMOS工藝制造的低功率邏輯芯片。這些芯片如果遭遇足夠高的靜電放電(ESD)電壓,芯片內(nèi)部的電介質(zhì)上就會(huì)產(chǎn)生電弧,并在門氧化物層燒出顯微鏡可見(jiàn)的孔洞,造成芯片的永久

2013-12-27 16:21:39

...............................................................................1ESD (Electrostatic Discharge) Protection in CMOS Integrated Circuits ..........................1目錄

2011-02-24 09:55:18

)靠近有相反電勢(shì)的集成電路(IC)時(shí),電荷“跨接”,引起靜電放電(ESD)。ESD以極高的強(qiáng)度很迅速地發(fā)生,通常將產(chǎn)生足夠的熱量熔化半導(dǎo)體芯片的內(nèi)部電路,在電子顯微鏡下外表象向外吹出的小?彈孔,引起即時(shí)

2016-07-22 11:26:49

隨著半導(dǎo)體工藝的飛速發(fā)展和芯片工作頻率的提高,芯片的功耗迅速增加,而功耗增加又將導(dǎo)致芯片發(fā)熱量的增大和可靠性的下降。因此,功耗已經(jīng)成為深亞微米集成電路設(shè)計(jì)中的一個(gè)重要考慮因素。為了使產(chǎn)品更具競(jìng)爭(zhēng)力

2019-10-14 07:48:14

常見(jiàn)ESD保護(hù)元件可分為哪幾類?不同便攜應(yīng)用的ESD保護(hù)解決方案

2021-06-08 06:15:34

深亞微米的CMOS工藝制造高速分頻器。由于CMOS器件的價(jià)格低廉,因而高速CMOS分頻器有著廣闊的市場(chǎng)前景。那分頻電路由什么構(gòu)成?你們知道2.4GHz動(dòng)態(tài)CMOS分頻器設(shè)計(jì)難嗎?

2021-04-07 06:17:39

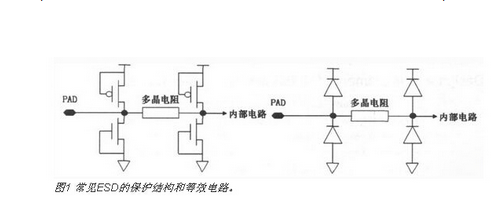

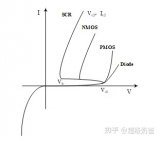

ESD(靜電放電)是CMOS電路中最為嚴(yán)重的失效機(jī)理之一,嚴(yán)重的會(huì)造成電路自我燒毀。論述了CMOS集成電路ESD保護(hù)的必要性,研究了在CMOS電路中ESD保護(hù)結(jié)構(gòu)的設(shè)計(jì)原理,分析了該結(jié)構(gòu)對(duì)版圖的相關(guān)要求,重點(diǎn)討論了在I/O電路中ESD保護(hù)結(jié)構(gòu)的設(shè)計(jì)要求。

2021-04-02 06:35:57

,提高了芯片的運(yùn)算速度。 但是,隨著工藝的進(jìn)步和尺寸的減小,靜電釋放(ESD),Elecyro Static Discharge)問(wèn)題變得日益嚴(yán)峻。據(jù)統(tǒng)計(jì),在集成電路設(shè)計(jì)中大約40%的失效電路是ESD問(wèn)題造成的。如何設(shè)計(jì)ESD保護(hù)電路?這個(gè)問(wèn)題急需解決。

2019-08-07 06:24:17

隨著微電子技術(shù)和半導(dǎo)體工業(yè)的不斷創(chuàng)新和發(fā)展,超大規(guī)模集成電路和集成度和工藝水平不斷提高,深亞微米(deep-submicron)工藝,如0.18μm、0.13μm已經(jīng)走向成熟,使得在一個(gè)芯片上完成系統(tǒng)級(jí)的集成已成為可能。

2019-10-30 07:55:52

關(guān)鍵芯片組外部ESD保護(hù)要求硅ESD保護(hù)技術(shù)與無(wú)源ESD保護(hù)技術(shù)比較消除信號(hào)完整性問(wèn)題的PicoGuard XS ESD保護(hù)技術(shù)智能手機(jī)等便攜及消費(fèi)產(chǎn)品電路保護(hù)及濾波應(yīng)用示例

2021-04-09 06:55:32

版本已經(jīng)過(guò)第三方實(shí)驗(yàn)室驗(yàn)證。 產(chǎn)品特點(diǎn)及其優(yōu)點(diǎn)l CMOS霍爾IC技術(shù)l 強(qiáng)大的抗RF噪聲技術(shù)l 工作電壓2.5至6V,適用于電池供電的應(yīng)用l 全極霍爾開(kāi)關(guān)微功耗l 高靈敏度可替換簧片開(kāi)關(guān)l 125

2019-11-07 14:46:47

領(lǐng)先水平,由深圳市明微電子有限公司負(fù)責(zé)該芯片的市場(chǎng)推廣及售后服務(wù)工作。SM9613是3對(duì)輸入4聲道輸出數(shù)字音頻控制處理芯片,該芯片采用深亞微米CMOS工藝技術(shù)制造,芯片內(nèi)部包含音量、低音、高音、通道均衡

2011-03-07 21:49:30

首創(chuàng)。集成式固態(tài)ESD保護(hù)是專有的ADI技術(shù),可實(shí)現(xiàn)非常高的ESD保護(hù)同時(shí)對(duì)MEMS開(kāi)關(guān)RF性能影響最小。圖3顯示了采用SMD QFN封裝的ESD保護(hù)元件。其中,芯片安放在MEMS芯片上,通過(guò)焊線連接

2018-11-01 11:02:56

本文選擇了SoC芯片廣泛使用的深亞微米CMOS工藝,實(shí)現(xiàn)了一個(gè)10位的高速DAC。該DAC可作為SoC設(shè)計(jì)中的IP硬核,在多種不同應(yīng)用領(lǐng)域的系統(tǒng)設(shè)計(jì)中實(shí)現(xiàn)復(fù)用。

2021-04-14 06:22:33

近年來(lái),有關(guān)將CMOS工藝在射頻(RF)技術(shù)中應(yīng)用的可能性的研究大量增多。深亞微米技術(shù)允許CMOS電路的工作頻率超過(guò)1GHz,這無(wú)疑推動(dòng)了集成CMOS射頻電路的發(fā)展。目前,幾個(gè)研究組已利用標(biāo)準(zhǔn)

2019-08-22 06:24:40

和低功耗設(shè)計(jì)、設(shè)計(jì)驗(yàn)證、芯片測(cè)試和可測(cè)性設(shè)計(jì)等主題,著重探討了深亞微米數(shù)字集成電路設(shè)計(jì)面臨的挑戰(zhàn)和啟示。本書可作為高等院校電子科學(xué)與技術(shù)(包括微電子與光電子)、電子與信息工程、計(jì)算機(jī)科學(xué)與技術(shù)、自動(dòng)化等

2009-02-12 09:51:07

深亞微米CMOS工藝中,I/O單元的實(shí)現(xiàn)可以從235微米減小到160微米和138微米。 這種新的設(shè)計(jì)方法在ESD防護(hù)性能和效率上都很大程度提高,并且在實(shí)現(xiàn)防靜電保護(hù)避免IC損壞,進(jìn)一步提高晶圓使用的效率方面發(fā)揮了積極作用。參考資料:防靜電資訊網(wǎng)

2012-12-11 13:39:47

新型互補(bǔ)電容耦合ESD保護(hù)電路的設(shè)計(jì)提出了一種改進(jìn)型的基于亞微米工藝中ESD 保護(hù)電路, 它由互補(bǔ)式電容實(shí)現(xiàn), 結(jié)構(gòu)與工藝簡(jiǎn)單。電路采用0.6μm1P2MCMOS 工藝進(jìn)行了驗(yàn)證, 結(jié)果表明

2009-12-23 16:33:58

。從成本效益比的角度來(lái)看,這已經(jīng)被證明是件很難做到的事。從圖1可以看出,隨著制造技術(shù)轉(zhuǎn)向90nm以下,將ESD保護(hù)水平維持在2,000V的成本,已開(kāi)始以指數(shù)級(jí)上升。因此,現(xiàn)在新的目標(biāo)是降低芯片上

2019-05-22 05:01:12

IC。在一個(gè)新的模塊快速連接該器件和ESD測(cè)試開(kāi)始獲得好的結(jié)果,因?yàn)镾ZESD9101成功保護(hù)了GPS通過(guò)所需的8kV存在等級(jí)。有了推薦的ESD保護(hù)器件、TLP的結(jié)果以及向上層管理報(bào)告8kV通過(guò)結(jié)果

2018-10-25 09:02:26

部芯片造成損傷片上ESD 保護(hù)電路。圖3相信所有人都希望ESD 防護(hù)能完全地集成到IC 芯片內(nèi)部,因?yàn)檫@樣會(huì)節(jié)省的板級(jí)空間,減少系統(tǒng)成本并降低設(shè)計(jì)與布線的復(fù)雜度。但從目前情況來(lái)看,前景并不樂(lè)觀。如今

2017-07-31 14:59:33

【作者】:張科營(yíng);郭紅霞;羅尹虹;何寶平;姚志斌;張鳳祁;王園明;【來(lái)源】:《原子能科學(xué)技術(shù)》2010年02期【摘要】:采用TCAD工藝模擬工具按照等比例縮小規(guī)則構(gòu)建了從亞微米到超深亞微米級(jí)7種

2010-04-22 11:50:00

,不普通數(shù)字電路更容易遭到損壞,因?yàn)橛糜?b class="flag-6" style="color: red">ESD保護(hù)的傳輸入保護(hù)結(jié)構(gòu)會(huì)增加輸入泄露,因此不能使用。所有ESD敏感器件均采用保護(hù)性封裝。IC通常裝在導(dǎo)電泡沫中或者防靜電包裝套管中,而后將容器密封在一個(gè)靜電

2018-01-16 14:21:19

解讀ESD靜電抑制器 因?yàn)橐蟾呒啥取⒖焖俣群托◇w積,如今的新興電子產(chǎn)品都使用基于先進(jìn)深次微米制程的芯片。但制程越先進(jìn),芯片對(duì) ESD 耐受度也就越差。當(dāng)這些電子產(chǎn)品在實(shí)際環(huán)境下受到 ESD沖擊

2013-12-11 15:58:03

使用液晶電視等HDMI終端設(shè)備支持的音頻/視頻格式。 HDMI接收器和發(fā)射器的IC芯片全部采用深亞微米工藝制造。亞微米CMOS制程十分敏感,通常設(shè)有ESD保護(hù)限制(最高2kV),必須符合人體放電模式

2019-06-17 05:00:06

摩爾定律對(duì)先進(jìn)CMOS IC的ESD保護(hù)的影響 持續(xù)不斷的特征尺寸小型化趨勢(shì),已經(jīng)使半導(dǎo)體制造商能夠在過(guò)去幾十年中通過(guò)把幾十億三極管集成到單一芯片之中來(lái)提高芯片性能、降低功耗及驅(qū)動(dòng)成本的下降。盡管

2018-12-05 10:39:44

隨著現(xiàn)代社會(huì)的飛速發(fā)展,我們對(duì)電子設(shè)備的依賴與日俱增.現(xiàn)代電腦越來(lái)越多的采用低功率邏輯芯片,由于MOS的電介質(zhì)擊穿和雙極反向結(jié)電流的限制,使這些邏輯芯片對(duì)ESD非常敏感。大多數(shù)USB集成電路都是

2019-08-02 17:43:22

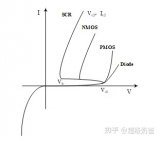

CMOS工藝中GG2NMOS結(jié)構(gòu)ESD保護(hù)電路設(shè)計(jì):采用GG2NMOS 結(jié)構(gòu)的ESD 保護(hù)電路的工作原理和對(duì)其進(jìn)行的ESD 實(shí)驗(yàn),提出了一種保護(hù)電路的柵耦合技術(shù)方案,并達(dá)到了預(yù)期效果. 通過(guò)實(shí)驗(yàn)可以看出其性

2009-11-20 14:48:43 41

41 本文研究了在CMOS 工藝中I/O 電路的 ESD 保護(hù)結(jié)構(gòu)設(shè)計(jì)以及相關(guān)版圖的要求,其中重點(diǎn)討論了PAD 到VSS 電流通路的建立。關(guān)鍵詞:ESD 保護(hù)電路,ESD 設(shè)計(jì)窗口,ESD 電流通路Constru

2009-12-14 10:45:54 55

55 本文采用 MEDICI 作為集成電路ESD 保護(hù)常用器件—柵極接地N 型MOS 管(GGNMOS)ESD 性能分析的仿真工具,綜合分析了各種對(duì)GGNMOS 的ESD 性能有影響的因素,如襯底摻雜、柵長(zhǎng)、接觸

2009-12-14 10:59:02 22

22 和艦科技自主創(chuàng)新研發(fā)的0.16 微米硅片制造工藝技術(shù)在原有比較成熟的0.18 微米工藝技術(shù)基礎(chǔ)上,將半導(dǎo)體器件及相關(guān)繞線尺寸進(jìn)行10%微縮(實(shí)際尺寸為0.162 微米),大大降低了芯

2009-12-14 11:23:36 25

25 超深亞微米IC設(shè)計(jì)中的天線效應(yīng)李蜀霞 劉輝華 趙建明 何春(電子科技大學(xué)電子電子科學(xué)技術(shù)研究院 成都 610054)【摘要】本文主要分析了超深亞微米集成電路設(shè)計(jì)中天線效應(yīng)

2009-12-19 14:54:53 45

45 一種全新的深亞微米IC設(shè)計(jì)方法

本文分析了傳統(tǒng)IC設(shè)計(jì)流程存在的一些缺陷,并且提出了一種基于Logical Effort理論的全新IC設(shè)計(jì)方法。

眾所周知,傳統(tǒng)的IC設(shè)計(jì)流

2009-12-27 13:28:50 615

615

目前幾乎所有的芯片組都有片上ESD保護(hù)。ESD電路放在芯片的外圍和鄰近I/O焊墊處,它用于在晶圓制造和后端裝配流程中保護(hù)芯片組。在這些環(huán)境中,ESD可通過(guò)設(shè)備或工廠的生產(chǎn)線工作人員引入到芯片組上

2011-02-18 10:29:07 942

942

,了解保護(hù)元件的特性知識(shí)也非常必要,需要考慮的重要因素之一是器件的箝位電壓。所謂箝位電壓是在ESD器件里跨在瞬變電壓消除器(TVS)上的電壓,它是被保護(hù)IC的應(yīng)變電壓。?因?yàn)槔孟冗M(jìn)工藝技術(shù)制造的IC

2018-11-22 16:58:54 826

826 ESD保護(hù)電路的設(shè)計(jì)目的就是要避免工作電路成為ESD的放電通路而遭到損害,保證在任意兩芯片引腳之間發(fā)生的ESD,都有適合的低阻旁路將ESD電流引入電源線。這個(gè)低阻旁路不但要能吸收ESD電流,還要能箝位工作電路的電壓,防止工作電路由于電壓過(guò)載而受損。

2019-03-04 14:24:01 4168

4168

ESD保護(hù)電路的設(shè)計(jì)目的就是要避免工作電路成為ESD的放電通路而遭到損害,保證在任意兩芯片引腳之間發(fā)生的ESD,都有適合的低阻旁路將ESD電流引入電源線。這個(gè)低阻旁路不但要能吸收ESD電流,還要能箝位工作電路的電壓,防止工作電路由于電壓過(guò)載而受損。

2019-04-08 15:26:11 2192

2192

隨著CMOS集成電路產(chǎn)業(yè)的高速發(fā)展,越來(lái)越多的CMOS芯片應(yīng)用在各種電子產(chǎn)品中,但在電子產(chǎn)品系統(tǒng)的設(shè)計(jì)過(guò)程中,隨著CMOS工藝尺寸越求越小,單位面積上集成的晶體管越來(lái)越多,極大地降低了芯片的成本

2020-12-30 10:28:00 2

2 ESD保護(hù)設(shè)計(jì)隨著CMOS工藝的演進(jìn)而越來(lái)越困難,迄今已有六百多件ESD相關(guān)的美國(guó)專利。而且,ESD更應(yīng)當(dāng)從芯片全局考慮,而不只是Input PAD,Output PAD,或Power PAD的問(wèn)題。

2021-03-17 22:28:55 25

25 當(dāng)持續(xù)時(shí)間更長(zhǎng)的 EOS 事件發(fā)生時(shí),沖擊 ESD 保護(hù)單元的能量就會(huì)更多,常常超出 ESD 保護(hù)單元的最大沖擊能量承受能力,這樣就會(huì)在 ESD 保護(hù)單元中積累太多的熱量,最終導(dǎo)致嚴(yán)重的毀滅性結(jié)果。

2022-04-20 09:22:39 2219

2219 電子發(fā)燒友網(wǎng)站提供《ESD保護(hù)芯片CH412技術(shù)手冊(cè).pdf》資料免費(fèi)下載

2022-09-09 11:29:03 1

1 靜電放電(ESD)會(huì)對(duì)集成電路(IC)造成破壞性的能量沖擊,良好的IC設(shè)計(jì)能夠在IC裝配到應(yīng)用電路的過(guò)程中保護(hù)IC免遭ESD沖擊的破壞。安裝后,IC還必須能夠承受ESD穿過(guò)靜電防護(hù)電路進(jìn)入最終電路

2023-06-10 15:40:58 582

582

點(diǎn)擊上方“藍(lán)字”關(guān)注我們!IC片上保護(hù)設(shè)計(jì)對(duì)EOS的影響全面的方法可以減少與EOS相關(guān)的故障通常理解的是,芯片上ESD保護(hù)是必不可少的,以滿足人體模型(HBM)和充電裝置模型產(chǎn)品合格(CDM)ESD

2021-12-31 16:08:02 1316

1316

靜電保護(hù)器件、ESD保護(hù)芯片,是一種高效型的靜電保護(hù)器件。在各類通信端口、接口中,經(jīng)常需要用到ESD靜電保護(hù)器件為其保駕護(hù)航,以品牌廠家東沃電子ESD靜電保護(hù)器件

2022-03-30 10:37:50 1285

1285

Resistor不單獨(dú)用于芯片的ESD保護(hù),它往往用于輔助的ESD保護(hù),如芯片Input第一級(jí)保護(hù)和第二級(jí)保護(hù)之間的限流電阻。如圖5,當(dāng)ESD電流過(guò)大,第一級(jí)ESD器件難以將電壓鉗位至安全區(qū)域時(shí),第二級(jí)ESD器件的導(dǎo)通將使其與電阻分壓,從而進(jìn)一步降低進(jìn)入內(nèi)部電路的電壓。

2023-12-07 09:15:04 516

516

靜電放電(ESD)是電子設(shè)備中一種常見(jiàn)的危害,它可能導(dǎo)致集成電路(IC)的損壞。對(duì)于CMOS IC來(lái)說(shuō),經(jīng)受過(guò)嚴(yán)重ESD電擊的可靠性會(huì)降低。

2023-12-15 15:32:09 219

219 靜電保護(hù)器件(ESD) 是由一個(gè)或多個(gè) TVS 晶粒采用不同的電路拓?fù)渲瞥删哂刑囟üδ艿亩嗦坊騿温?ESD 保護(hù)器件。

2024-02-17 16:01:00 571

571

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論