2011年泰國的洪水把機(jī)械硬盤的價格推高了不少,卻給SSD固態(tài)硬盤帶來了一個新的發(fā)展契機(jī),光刻技術(shù)與半導(dǎo)體技術(shù)的快速發(fā)展,也讓SSD的成本方面逐漸降低。隨著SSD在消費(fèi)級市場的普及,用戶也開始關(guān)心SSD存儲顆粒的相關(guān)技術(shù),讀者也渴望了解主流SSD存儲顆粒的相關(guān)知識。下面我們將向讀者解析目前MLC NAND顆粒所采用的技術(shù)并深度剖析最新的20nm存儲顆粒的結(jié)構(gòu)設(shè)計與生產(chǎn)工藝,最后重點(diǎn)講述下一代存儲顆粒的原理與發(fā)展?jié)摿Α?/p>

ONFI與Toggle DDR接口標(biāo)準(zhǔn)爭斗的白熱化

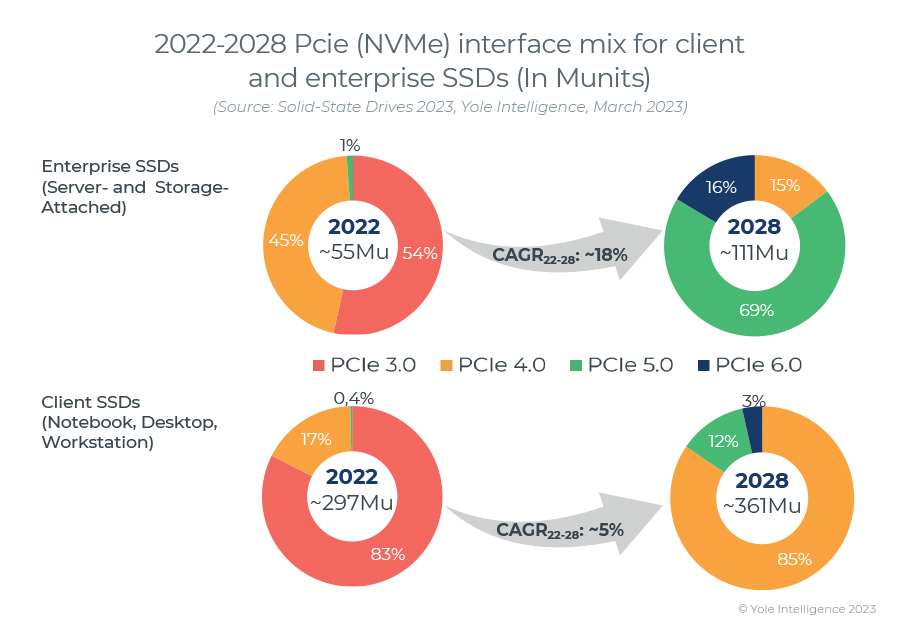

相信大多數(shù)用戶對SLC存儲顆粒與MLC存儲顆粒都有一定了解。MLC存儲顆粒與SLC存儲顆粒相比,以相同芯片面積上獲得兩倍存儲容量的成本優(yōu)勢迅速贏取了消費(fèi)級用戶的青睞。SLC存儲顆粒則退居追求高性能、穩(wěn)定性的企業(yè)級市場。雖然所有廠商的MLC存儲顆粒的原理基本相同,但因生產(chǎn)工藝與技術(shù)的不同,它們之間也存在著一定的差異。最大的差異就是存儲顆粒的接口標(biāo)準(zhǔn),以英特爾、美光、海力士為主的ONFI(Open NAND Flash Interface)接口標(biāo)準(zhǔn)聯(lián)盟;三星和東芝組成的Toggle DDR Model接口標(biāo)準(zhǔn)聯(lián)盟。

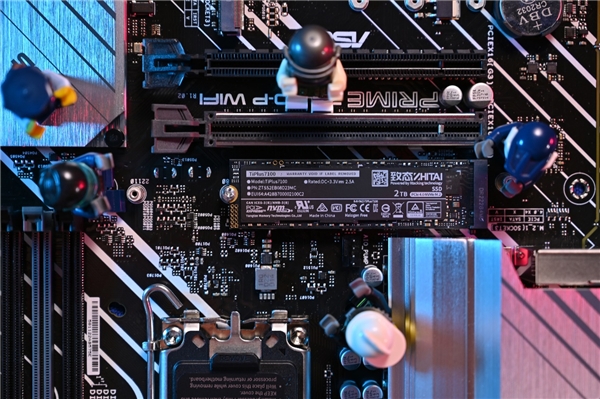

ONFI陣營全家福。

現(xiàn)在ONFI接口標(biāo)準(zhǔn)已經(jīng)發(fā)展到第三代,采用了DDR(Double Data Rate)信號技術(shù)與同步時鐘控制,傳輸帶寬達(dá)到了400MB/s。同時將SSD主控芯片中的ECC糾錯功能集成到了存儲顆粒內(nèi)部,增加了主控芯片的效率。Toggle DDR接口標(biāo)準(zhǔn)也發(fā)展到了第二代,它與前者最明顯的差別在于采用了異步時鐘控制。同步時鐘控制是主控可以通過發(fā)送同步指令激活閃存上的同步時鐘信號,使閃存與主控工作在同步模式,此時閃存的數(shù)據(jù)傳輸速率會大幅度提升。而Toggle DDR接口標(biāo)準(zhǔn)采用異步設(shè)計,異步時鐘控制在主控發(fā)出指令以后,主控與閃存之間有一個時鐘信號匹配的過程,然后再傳輸數(shù)據(jù)。

在理論上,異步時鐘控制的時間延遲肯定是落后同步時鐘控制。雖然如此,依靠三星和東芝在NAND方面的優(yōu)勢,Toggle DDR接口標(biāo)準(zhǔn)在各項技術(shù)產(chǎn)生上并沒有落后老牌的ONFI接口標(biāo)準(zhǔn),傳輸帶寬也達(dá)到了400MB/s。加上現(xiàn)在主控的技術(shù)差異,兩種接口標(biāo)準(zhǔn)的產(chǎn)品在實際測試體驗差別不大,玩家們也不需要糾結(jié)選擇何種存儲顆粒,只要選擇適合自己的就可以了。至于這兩種接口的實際體驗,可以參見《微型計算機(jī)》2012年6月下《“大”“快”人心,兩款512GB固態(tài)硬盤深度體驗》,兩款產(chǎn)品分別是采用了英特爾同步顆粒的OCZ Vertex 4 512GB固態(tài)硬盤和采用東芝Toggle DDR異步閃存顆粒的浦科特PX-512M3 512GB固態(tài)硬盤。

單就原理而言,毫無疑問ONFI的優(yōu)勢還是要強(qiáng)于Toggle DDR,這兩種接口標(biāo)準(zhǔn)的爭斗我們可以看做是對新技術(shù)的探索,它所帶來的技術(shù)革新的最終受益者仍然是消費(fèi)者。然而接口也只是SSD存儲顆粒的一小部分,最重要的仍然是存儲單元,在最小的芯片面積上集成最多的存儲容量才是解決SSD成本的根本原因。為了達(dá)到這一目的,廠商不斷縮小MLC的制程工藝,英特爾目前已經(jīng)將其工藝升級到了20nm。

英特爾20nm MLC的創(chuàng)新技術(shù)

日前英特爾發(fā)布了20nm MLC存儲顆粒樣品,它的芯片面積也減少了不少,以64Gb顆粒為例,20nm工藝的芯片面積為117mm2,英特爾25nm工藝同容量的芯片面積為162mm2,新工藝節(jié)約了約30%的芯片面積。當(dāng)然,這次升級并不只是在工藝上通過光刻來微小化存儲單元,結(jié)構(gòu)與材料上仍然發(fā)生一定的變化。25nm MLC存儲單元的控制柵(Control Gate)和絕緣膜纏繞在浮柵(Floating Gate)上,控制柵與浮柵重合面積絕大多數(shù)在側(cè)壁,耦合因子很大程度上也依賴于浮柵側(cè)壁。隨著存儲單元之間的距離越來近,多晶硅材質(zhì)的控制柵填入高深寬比的溝道已經(jīng)非常困難了,單元與單元之間的干擾也越來越大。

為了解決上面的問題,英特爾20nm工藝采用了平面浮柵與控制柵結(jié)構(gòu),這種結(jié)構(gòu)的浮柵與控制柵相比25m的柵結(jié)構(gòu)減薄了許多。從25nm與20nm剖面圖對比可以看出來,浮柵從陡峭的“高山”形狀轉(zhuǎn)變成了低矮的“長方形”的形狀,控制柵形狀也與浮柵類似了,這個結(jié)構(gòu)實現(xiàn)了我們常見的理想化NAND結(jié)構(gòu)。此時帶來的問題就是控制柵與浮柵的重合面積越來越小,耦合因子也減少。但高介電常數(shù)的IGD柵間絕緣材料與金屬控制柵(下簡稱金屬柵)的引入很巧妙地解決這個問題,目前對高介電常數(shù)的IGD比常用的ONO(Oxide-Nitride-Oxide)柵間絕緣材料擁有更高的K值,增加了控制柵對浮柵的耦合率。金屬控制柵相比多晶硅控制柵,電阻更低,導(dǎo)電能力更強(qiáng),形成的電場均勻度也好。讀者也許會問,如果金屬柵有這么多的好處,為什么之前沒有采用呢?這與半導(dǎo)體制造技術(shù)有關(guān),硅是半導(dǎo)體物質(zhì)(金屬是導(dǎo)體),它一旦沾附金屬離子(常見的Na+,F(xiàn)e2+),則芯片就會失效,半導(dǎo)體制造中的前段和后端作業(yè)就是以金屬工藝來作為分界線。而控制柵的工藝通常都是在前段作業(yè)完成,金屬柵的應(yīng)用必引來金屬離子污染,為整個芯片生產(chǎn)線帶來巨大的麻煩。

總體而言英特爾20nm存儲顆粒給我們還是帶來了較多的驚喜,更小的工藝帶來更小的芯片面積,成本也自然會下降。截止發(fā)稿為止,有關(guān)20nm MLC的產(chǎn)品測試顯示其性能較25nm產(chǎn)品有所下降。這也在意料之中,小的浮柵電荷存儲減少,這將需要更靈敏的控制柵的來判斷浮柵中是否存儲有“數(shù)據(jù)”,同時在出錯率方面也會大大增加,從而需要更強(qiáng)的糾錯功能,這為讀寫速度帶來了一定的拖累。

英特爾25nm與20nm剖面圖以及理想的NAND結(jié)構(gòu)。

SSD存儲顆粒的未來

客觀一點(diǎn)看,這次英特爾發(fā)布的20nm MLC存儲顆粒只是減少了芯片面積,控制了芯片成本,而沒有從根本上解決目前存儲顆粒的讀寫速度與壽命;從原理層面來看,只要是基于EEPROM原理的NAND永遠(yuǎn)也逃脫不了低壽命、低穩(wěn)定性的宿命。要么徹底改變存儲單元的存儲原理,要么新的材料出現(xiàn),這樣才能徹底拯救SSD,下面我們將來看幾種可能取代目前NAND Flash的下一代SSD存儲顆粒技術(shù)。

受材料束縛的FeRAM

我們知道MLC的浮柵技術(shù)需使用高電壓,迫使電荷穿過致密柵氧化層進(jìn)出浮柵達(dá)到擦寫目的。高寫入功率和長期的寫操作,電荷不停穿梭于柵氧化層,就像離子轟擊一樣,這對柵氧化層造成物理性傷害。柵氧化層一旦被轟擊得“蓬松”,它就會失去“困住”浮柵中電子的能力,那么存儲單元就失去了作用。而FeRAM采用與DRAM一樣的結(jié)構(gòu),基本單元由一個MOS管與平面電容組成,平面電容強(qiáng)大的充放電能力帶來無窮次讀寫能力與強(qiáng)悍的讀寫速度,看看通過軟件將DRAM轉(zhuǎn)變成SSD的讀寫能力就知道了。但DRAM斷電以后就會失去數(shù)據(jù),它的罪魁禍?zhǔn)资莾?nèi)部平面電容電介質(zhì)材料無法存儲電荷,在斷電以后它就會迅速放電,失去存儲能力。FeRAM將平面電容的電介質(zhì)材料換成了具有存儲功能的鐵電晶體,當(dāng)在平面電容中加電壓時,鐵電晶體在電場作用下,大量中心原子在晶體單胞中移動耦合形成鐵電疇,鐵電疇在電場作用下形成極化電荷。鐵電疇在反向電壓下所形成的極化電荷較高,鐵電疇在正向電壓下所形成的極化電荷較低,在斷電以后也能保持各自的狀態(tài),這種鐵電材料的二元穩(wěn)定狀態(tài)使得鐵電晶體可以作為存儲器。

目前這種鐵電晶體主要有PZT(鋯鈦酸鉛)、SBT(鉭酸鍶鉍)兩種材質(zhì)。PZT使用最廣泛,它的優(yōu)點(diǎn)是能夠在較低的溫度下制備,如濺射和MOCVD,原材料便宜、晶化溫度較低,工藝集成較容易;但有疲勞退化問題,而且鉛會對環(huán)境造成污染。SBT最大的優(yōu)點(diǎn)是沒有疲勞退化的問題,而且不含鉛;它的缺點(diǎn)是制作工藝溫度較高,工藝集成難度很大。另外它們最致命的缺點(diǎn)就是在結(jié)構(gòu)微小化方面有很大的問題,采用納米級的工藝較難實現(xiàn)。

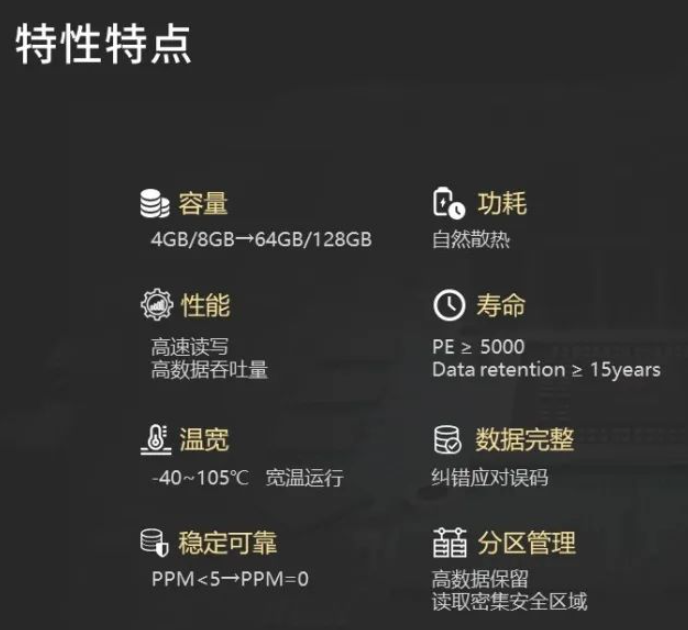

FeRAM現(xiàn)在已經(jīng)廣泛運(yùn)用在工業(yè)控制,單片機(jī)與嵌入式系統(tǒng)中。它與傳統(tǒng)的DRAM結(jié)構(gòu)太相似,這在芯片面積上較MLC NAND還是有很大的劣勢,從DRAM內(nèi)存的容量就可以看出來。受制于材料與生產(chǎn)工藝問題,目前FeRAM應(yīng)用于大容量存儲的幾率仍然不大。

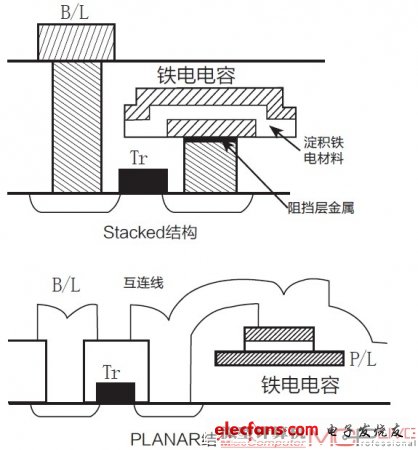

兩種不同結(jié)構(gòu)的FeRAM,Planar結(jié)構(gòu)的工藝相對簡單,其隔離采用LOCOS結(jié)構(gòu),且不需要使用CMP(化學(xué)機(jī)械平坦化)。而Stacked結(jié)構(gòu)的集成度較高,但是所用工藝相對先進(jìn),隔離采用STI,需要使用CMP,并可以使用銅工藝來制作導(dǎo)線。

寡助的PRAM

PRAM與DRAM、FeRAM在結(jié)構(gòu)上還是有相似之處,它在平板電容部分做了結(jié)構(gòu)型調(diào)整,采用了GST結(jié)晶體作為存儲核心,并為結(jié)晶體配備了一個加熱器。通過加熱器對結(jié)晶體進(jìn)行加熱控制結(jié)晶體狀態(tài),在結(jié)晶體狀態(tài)下呈現(xiàn)低電阻狀態(tài),加熱后呈現(xiàn)非結(jié)晶體高電阻狀態(tài)。由于是晶體結(jié)構(gòu),在斷電以后也能夠長時間保持晶體狀態(tài),以此表示存儲“0”和“1”。這種結(jié)構(gòu)的讀寫速度與目前DRAM相當(dāng),只是在微小化方面較DRAM有很大提高,理論上這種結(jié)晶體能夠微小化到5nm,取代目前MLC NAND的可能性也較大。只是目前力挺PRAM只有三星和IBM等少數(shù)廠商,技術(shù)發(fā)展?jié)摿^MLC NAND還是有很大的弱勢,目前它還停留在研發(fā)和試驗階段。

PRAM結(jié)構(gòu)圖

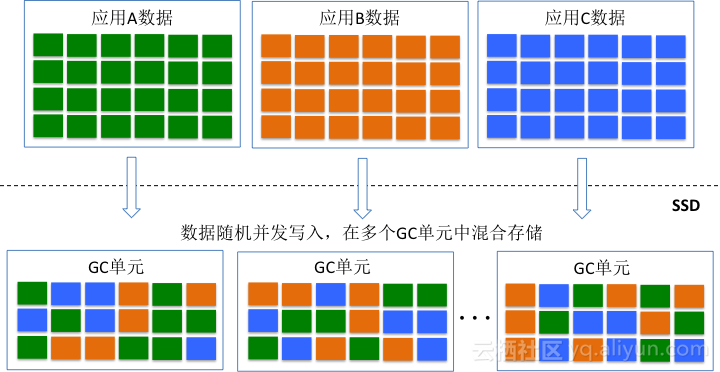

離我們最近的3D NAND

前面兩種新存儲結(jié)構(gòu)在目前應(yīng)用于大容量存儲還不夠成熟,東芝、三星與海力士決定通過新技術(shù)將MLC NAND的壽命延長,畢竟在MLC NAND的資金投入太大。3D,無論在電影還是半導(dǎo)體行業(yè)都成了熱門詞匯,Ivy Bridge處理器讓大家初步認(rèn)識了3D晶體管,現(xiàn)在3D NAND技術(shù)也浮出了水面。東芝、三星與海力士都提出了各自的3D結(jié)構(gòu),預(yù)計在未來三年投入市場,到時候存儲顆粒將呈現(xiàn)“百家爭鳴”的狀態(tài),現(xiàn)在我們以三星和東芝3D結(jié)構(gòu)來先睹3D NAND的魅力。

3種3D構(gòu)圖

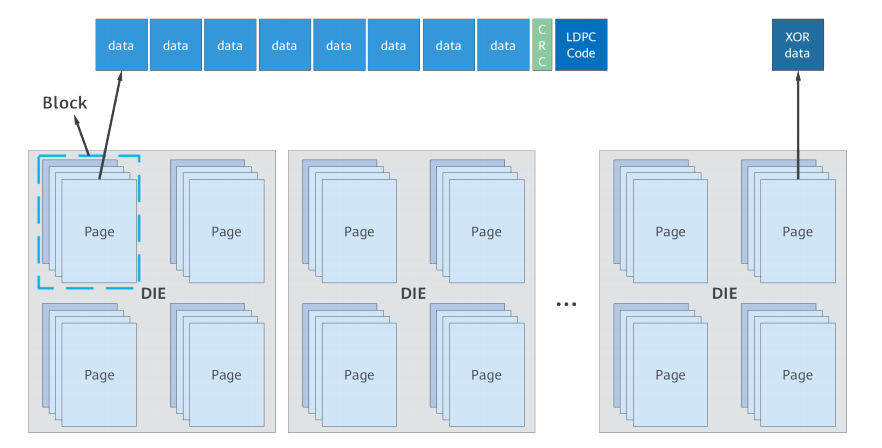

從3D構(gòu)圖可以看出,東芝P-BICS與三星TCAT結(jié)構(gòu)看起來完全不一樣,其實它們原理是一樣的。首先通過交替淀積多個氧化層和氮化層的方法形成疊層,然后使用濕法蝕刻將疊層中的氮化硅(即氮化層)蝕刻掉,最后填充鎢材料形成字線(Word line),位線(Bit line)及觸點(diǎn)結(jié)構(gòu)。

可能單就講解讓讀者看起來較抽象,先看看結(jié)構(gòu)圖(制造流程圖),前面我們講過它是交替淀積多個氧化層和氮化層,圖中的灰色部分就是氧化層(Oxide film),黃色就是氮化層(Nitride film),通過干法蝕刻挖出字線(Word line)。然后利用濕法蝕刻掉氮化層,在氮化層部位構(gòu)建金屬控制柵。那么它的存儲單元在哪兒呢?就在金屬柵周圍,只是存儲單元不再是多晶硅的浮柵,而是換成了氮化硅(SiN)。氮化硅因為結(jié)構(gòu)特殊,電荷往往會自動積聚到它的晶格周圍,有點(diǎn)像靠某種手段強(qiáng)制收集電荷的意思,所以三星將這種結(jié)構(gòu)就命名為電荷捕獲型柵級結(jié)構(gòu)。從圖中(三星3D結(jié)構(gòu)單元圖)我們可以看到在金屬柵下面由Al2O3致密氧化物作為與存儲單元的隔絕層,底部SiO2是電子穿越層,電子穿過SiO2進(jìn)入氮化硅而積聚電荷。

制造流程圖

看起來這種結(jié)構(gòu)非常的完美,存儲單元也很多,但實現(xiàn)起來卻非常困難。首先是挖高深寬比的深溝槽問題,由于蝕刻問題,較難實現(xiàn)絕對垂直。其次是它內(nèi)部結(jié)構(gòu)有凹槽,問題就在于往內(nèi)部生長致密氧化膜和填充金屬柵,高深寬比溝槽必然造成底部與頂部的反應(yīng)物質(zhì)不均性,凹槽內(nèi)的膜厚與表面凹槽內(nèi)的膜厚肯定會不一樣。而且高深寬比溝槽在填充金屬柵的時候也容易出現(xiàn)“空洞”,這在半導(dǎo)體制造中絕對是個大忌。不過這種結(jié)構(gòu)還有一個好處就是可以利用過時的制造工藝實現(xiàn),如50nm工藝,而且生產(chǎn)線投入也沒有20nm級工藝大。利用50nm制造出的產(chǎn)品在相同面積上的容量上完全可以趕上現(xiàn)在20nm MLC NAND容量,這樣一來存儲顆粒的成本也就降下來了。

三星3D結(jié)構(gòu)單元圖

大勢所趨的ReRAM

相信PC硬件迷們都是知道,最初的機(jī)械硬盤體積很大,容量也只有幾十兆。巨磁效應(yīng)的發(fā)現(xiàn)讓機(jī)械硬盤容量有了質(zhì)的飛躍,而垂直記錄技術(shù)的應(yīng)用讓機(jī)械硬盤容量繼續(xù)呈線性增長,目前消費(fèi)級機(jī)械硬盤已經(jīng)達(dá)到了4TB。SSD固態(tài)硬盤呢?有什么東西讓它在容量上也像機(jī)械硬盤那樣飛躍呢?

3D結(jié)構(gòu)的ReRAM。

答案是憶阻器(Memristor)或者叫記憶式電阻。關(guān)于ReRAM的發(fā)展和應(yīng)用,在《微型計算機(jī)》8月上的《記憶式電阻—顛覆PC架構(gòu)的革命?》做了介紹,這里只補(bǔ)充一點(diǎn)它的基本原理、材質(zhì)與相關(guān)大容量存儲方案。憶阻器的結(jié)構(gòu)非常簡單,與二極管極為相似(只是材料為TiO2)。以TiO2為兩個漂移區(qū),一側(cè)為正常成分的TiO2,一側(cè)為少氧的TiO2(寫為TiO2-x)。當(dāng)從左側(cè)通正電壓,由于電場作用,右側(cè)TiO2-x中的電子運(yùn)動到TiO2中,然而TiO2-x中因為結(jié)構(gòu)組成而缺少電子,電子向左側(cè)運(yùn)動后,右側(cè)完全形成了耗盡區(qū),相當(dāng)于右側(cè)成了一個斷路,整個狀態(tài)呈現(xiàn)高阻態(tài)。當(dāng)右側(cè)TiO2-x帶正電,在電場的影響之下,TiO2中電子向TiO2-x運(yùn)動,補(bǔ)充TiO2-x本來就缺少的電子,讓整個狀態(tài)呈現(xiàn)一種平衡狀態(tài),電阻也低。在斷電情況下這種材料能夠完全記憶各自的狀態(tài),且不需要晶格變化。通過控制電流的變化就可改變其阻值,如果把高阻值定義為“1”,低阻值定義為“0”,則這種電阻就可以實現(xiàn)存儲數(shù)據(jù)的功能,而且電流流過就能立馬實現(xiàn)讀寫,讀寫時間延遲很小。

研究人員利用這種材料研究出了網(wǎng)格交叉存儲單元,就像圍棋的交叉格,上下兩集電路,交叉點(diǎn)利用憶阻器作為存儲單元,每個交叉點(diǎn)就一個存儲單元,只需要計算存儲點(diǎn)的坐標(biāo)位置就可以很快實現(xiàn)讀寫定位。存儲單元沒有了其他的元件,完全能夠解決面積問題,而且能夠微小化到10nm以下。由于這種結(jié)構(gòu)簡單,工藝難度也非常小,沒有3D垂直的深溝槽,沒有內(nèi)部凹槽,但3D NAND的多層堆積也適用。所以ReRAM在芯片面積、容量方面、與工藝難度相對于3D NAND都有較大的優(yōu)勢,在大容量存儲方面的應(yīng)用前景無可限量。

電子發(fā)燒友App

電子發(fā)燒友App

評論