???? 頻率合成技術是指能由一個高穩定度和準確度的標準參考頻率,經過一系列的處理,產生大量離散的具有同一穩定度和準確度的信號頻率輸出,并且輸出信號的頻率可由數字信號控制改變,它主要的應用是為上/下變頻的中頻或射頻信號提供本振。頻率合成的基本方法有三種:直接頻率合成、鎖相式頻率合成以及直接數字頻率合成。鎖相式頻率綜合器是現今應用最為廣泛的一種頻率綜合器,它具有輸出頻率范圍大,雜散抑制特性好的特點。

??? 在短波數字接收系統中,從天線端接收到的短波信號與本振信號混頻得到70 MHz中頻,之后對中頻信號進行帶通采樣。本振信號的穩定性和準確度對系統性能有著重要和直接的影響。本文采用頻率合成技術,應用ADl公司的頻率綜合器ADF4111和Altera公司的FLEXlOKE系列FPGA實現頻率穩定,精度高,范圍為70~90 MHz,步進間隔1 MHz的數字鎖相式頻率源本振。

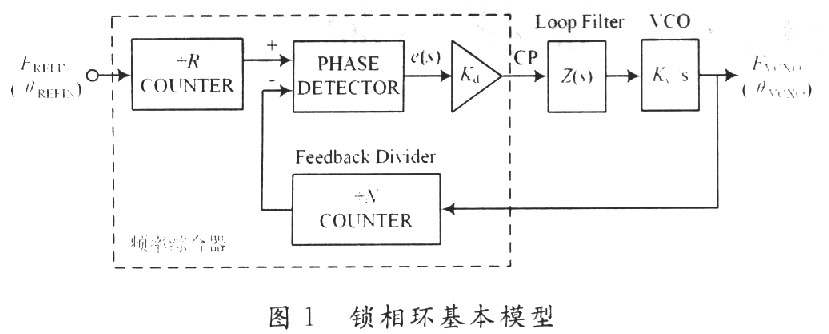

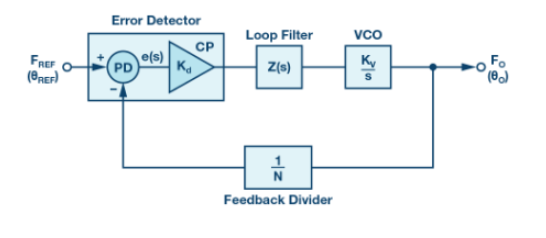

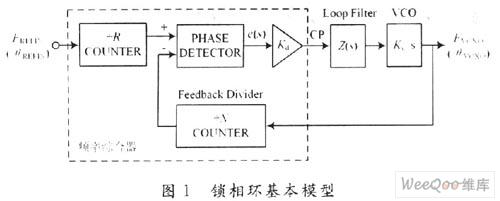

1 鎖相環基本原理

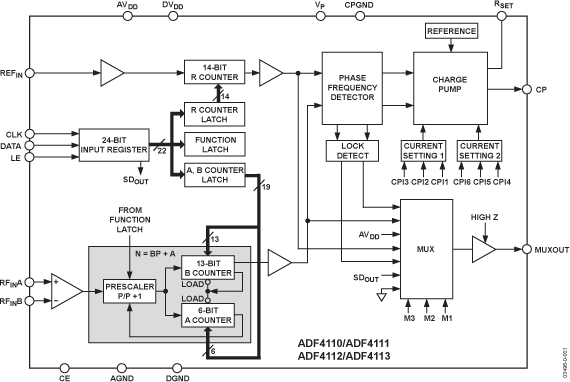

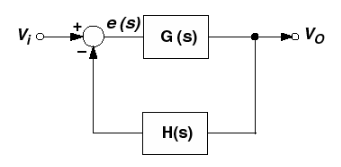

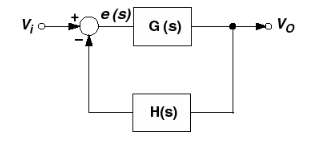

??? 鎖相環(PLL)是一種建立在相位負反饋基礎上的循環控制系統,如圖1所示。一個鎖相環由以下四部分組成:

??? (1)R分頻因子,鑒相器(Phase Detector),充電泵(Charge Pump)。

??? (2)環路濾波器,一般是低通濾波器,其作用是對充電泵的電流輸出進行濾波,以驅動壓控振蕩器,其傳輸因子為Z(s);

??? (3)壓控振蕩器,有一個頻率靈敏度Kv/s;

??? (4)反饋分頻因子N。

??? 它以一個高準確度,穩定度的晶體振蕩器的R分頻作為輸入參考頻率,該輸入參考頻率作為鑒相器的基準與壓控振蕩器輸出的進行比較,產生一個對應于兩個信號相位差的電流脈沖。該電流脈沖經環路濾波器積分產生一個控制電壓,并濾除其中的高頻分量和噪聲,這個電壓驅動壓控振蕩器(VCO)的輸出頻率增加或減少。當環路鎖定時輸入參考頻率與壓控振蕩器輸出的N分頻的頻差為零,相位差不再隨時間變化。這時控制電壓為一固定值,環路進入鎖定狀態。

??? 當輸入的參考時鐘fREFIN,壓控振蕩器的輸出fVCXO兩個頻率分別經R和N分頻后的頻率和相位均相同時,鑒相器的輸出e(s)為O,此時環路將處于鎖定狀態。由方程e(s)=FREFIN/R-FVCXO/N可以推導出,當e(s)=0時,fREFIN/R=FVCXO/N,即FVCXO=NFREIN/R。

??? 鎖相式頻率綜合器將R,N分頻因子、鑒相器、充電泵集成于一個芯片內,對相位噪聲和雜散等具有很好的抑制作用,而且調試簡單。它作為通信、雷達、遙測遙控、電子偵察等系統中的核心部件,是保證整個電子系統性能的關鍵因素之一,因而目前被廣泛應用于電視、儀表、通信等許多領域。

2 數字鎖相式頻率源設計方案

??? 根據系統需求,數字鎖相式頻率源設計指標主要為:輸出頻率為70~90 MHz;步進間隔為1 MHz;輸出功率為9 dBm。為了滿足這三個主要指標,設計從以下三方面考慮方案的設計和器件的選用。

2.1 輸出頻率

??? 為了得到輸出范圍為70~90 MHz的高精度頻率,設計中采用ADI公司推出的高性能鎖相頻率綜合器芯片ADF4111,其RF回饋輸入的最高頻率為1.2 GHz,即為鎖相環路可得到的最大輸出頻率,滿足本設計頻率輸出范圍要求。該芯片可用于無線射頻通信系統基站、無線局域網、手機,以及通信檢測設備中。它主要由四部分構成:

??? (1)低噪聲鑒頻相器(PFD)。

??? (2)精密充電泵(Charge Pump)。

??? (3)可編程預置分頻器。主要由三個可編程計數器組成:A計數器(6位)、B計數器(13位)、雙模預置分頻器(P/(P+1),P為預置分頻器的模),這三類計數器執行VCO輸出頻率到PFD的N分頻,實現N=BP+A的運算;其中雙模預置分頻器有四種工作模式:8/9,16/17,32/33,64/65;

??? (4)參考分頻器(R計數器,14位)。

??? 使用時需要配置寄存器,寄存器配置除了配置芯片工作方式外,主要是設置輸入時鐘分頻因子R和VCXO輸入分頻比A,B,使鑒相器的兩個輸入時鐘相等。VCXO輸出的時鐘與輸入時鐘關系為:FVCXO=[(P×B)+A]FREFIN/R。式中:P為prescaler因子;FREFIN和FVCXO分別是輸入的參考時鐘頻率和壓控振蕩器的輸出頻率。

??? 寄存器的配置可采用FPGA控制的方法。FPGA因其集成度高、功能強大、用戶可編程、體積小等特點被應用得越來越廣泛。在該設計中其對寄存器的配置也顯得靈活而方便。設計中選用Altera公司的0.25μmCMOS ROM工藝規程的結構的FLEX系列芯片EPFlOK50EQC240-3,FLEX系列的芯片是一種中等密度的器件,基于查找表結構,性能高,功耗低。FPGA的程序開發使用的是Altera公司的QuartusⅡ軟件實現的,用AHDL硬件描述語言編寫ADF4111的寄存器配置程序。

??? 與頻率綜合器ADF4111構成鎖相環的壓控振蕩器選用了Mini-circuit公司POS-100,它是一款性能優良的壓控振蕩器,其調諧電壓范圍是0~16 V,對應的輸出頻率范圍為45~110 MHz,電壓調節靈敏度為4.2~4.8 MHz/V,輸出功率的典型值為8.3 dBm,從其電壓一頻率關系得知,當輸出頻率為90 MHz時,對應的輸入電壓在11.5~12 V之間,而當給ADF4111的模擬和數字供電端加3.3 V電壓,電荷泵供電端加5 V電壓時,電荷泵輸出經環路濾波器后的電壓最高為5 V,該5 V電壓若不放大,顯然無法驅動壓控振蕩器產生90 MHz的頻率。為此,在環路濾波器后需要添置一個放大器,OP191是AD公司一款供電電壓為2.7~12 V的放大器,主要應用在工業控制,電訊,遠程感應等領域,將它的供電電壓設計為12 V,可以使其輸出電壓最高達到12 V,能夠滿足壓控振蕩器輸出頻率為90 MHz的調諧電壓輸入要求。

2.2 頻率步進

??? 實現頻率步進的方法是通過改變頻率綜合器ADF411l的寄存器配置值,從而調整壓控振蕩器的輸出頻率以達到環路的鎖定,最終實現壓控振蕩器輸出頻率的步進。

??? 頻率的步進既要使VCO輸出頻率升高又能使其降低,故設計中,采用兩個按鍵分別發起升高和降低的指令要求,并通過FPGA用AHDL編程實現相應的對ADF411l寄存器配置的指令。

2.3 輸出功率

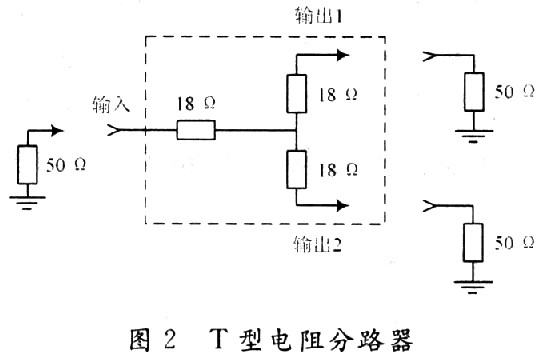

??? 根據信號流程,壓控振蕩器POS-100的輸出分為兩路:一路反饋于ADF4111,另一路作為本振輸出。此時,壓控振蕩器的輸出需要經過一個T型網絡分成兩路,這里T型網絡是一個電阻分路器,如圖2所示。它廣泛應用于一個源需要驅動兩個負載的情況,其目的是進行電路的阻抗匹配。常用三個18 Ω的電阻值連成Y型。如果其中的一個負載為50 Ω,它就相當于衰減6.3 dB的T型網絡。

?

??? 壓控振蕩器POS-100輸出功率的典型值為8.3 dBm,經過T型網絡后,作為本振輸出的信號功率為8.3-6.3=2 dBm,顯然2 dBm的信號需要放大,因此設計中采用Mini-circuits公司的單塊集成電路放大器ERA-4。它能夠放大的信號頻率范圍為0~4 GHz,對0~1 GHz信號的放大增益為14 dB。為確保ERA-4的本振輸入信號不飽和,設計中將2 dBm的本振信號經過了一個4 dB的衰減器后再輸入ERA-4。此時,從ERA-4輸出的本振信號功率為2-4+14=12 dBm。最終,為得到9 dBm的本振輸出,需要再將ERA-4輸出的信號衰減3 dB。衰減器的設計采用兀型電阻匹配網絡。

??? 系統中,FPGA的工作時鐘和頻率綜合器ADF4111輸入參考時鐘由美國WINTRON公司的40 MHz的TCXO時鐘提供。

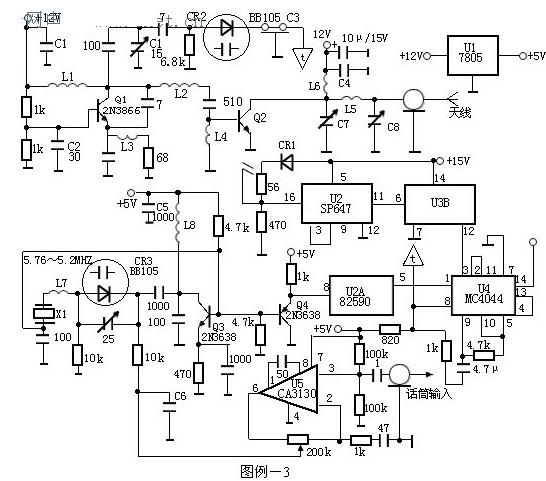

3 數字鎖相式頻率源硬件設計

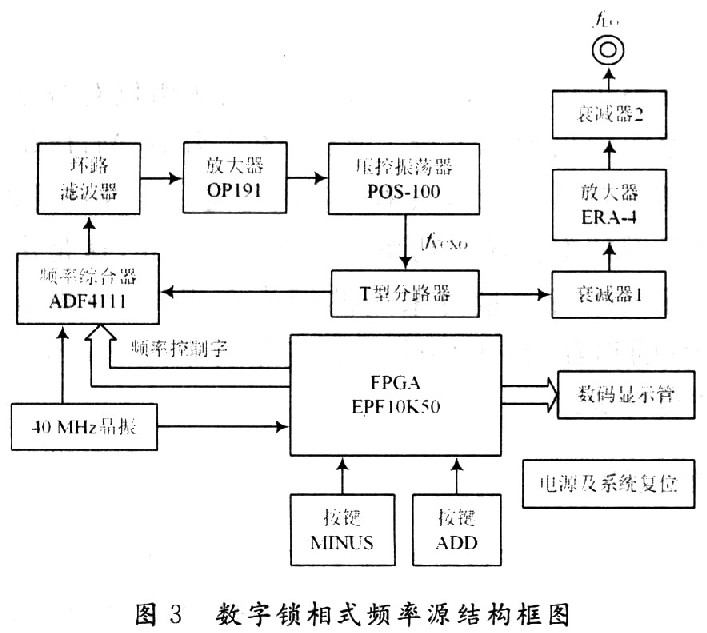

??? 根據數字鎖相式頻率源設計方案,設計的硬件結構如圖3所示。

??? 作為系統的邏輯控制中心,FLEXlOK50E芯片內部集成有50 000個門,2 880個邏輯單元(Logicelements),其RAM容量為40 960 b,它完成的功能主要有:

??? (1)接收按鍵的對輸出頻率fVCXO增減要求的指令;

??? (2)配置頻率綜合器ADF4111;

??? (3)控制數碼顯示管以顯示鎖定后的fVCXO值。

??? 鎖相環路的設計是保證系統能夠產生穩定,高精度的本振輸出的關鍵。從壓控振蕩器輸出的本振必須經過衰減器和放大器,以確保最終的本振輸出功率符合指標要求,下面重點闡述這兩部分的電路設計。

3.1 鎖相環電路設計

??? 鎖相環電路設計主要有兩部分:ADF4111設計和環路濾波器的設計,下面分別對這兩方面進行闡述。

3.1.1 ADF4111設計

??? ADF4111內部的四個24位控制字寄存器,分別為R分頻器、N分頻器、功能寄存器和初始化寄存器,FPGA對鎖相環的控制通過設置這四個控制寄存器的控制字來實現。

??? ADF4111從外部輸入的信號有標準頻率源信號(40 MHz)和FPGA輸出的控制信號。標準頻率源信號輸入到ADF4111后,經14位的R分頻器得到鑒相基準頻率并送至鑒相器。控制信號由時鐘信號CLK、數據信號DATA和使能信號LE組成。在CLK的控制下,由DATA信號端輸入24位數據信號,暫時存放在24位輸入寄存器中。在接收到LE后,先前輸入的24位數據根據地址位到達對應的鎖存器。當ADF4111接收到反饋回來的輸出頻率后,首先通過預分頻比例因子P,經A,B分頻器,得到分頻以后的回饋信號,之后輸入到鎖相器。與分頻以后的標準頻率源信號在鑒相器中比較,輸出低頻控制信號以控制外部VCO的頻率,使其鎖定在參考頻率的穩定度上。

??? 設計中采用40 MHz晶振作標準頻率源信號。為了得到1 MHz的步進量。ADF4111的PFD輸入頻率為l MHz。所以將參考時鐘分頻器R設置為40,此外,設置P=8。由關系式:FVCXO=[(P×B)+A]FREFIN/R知,當FVCXO=70 MHz時,可以設置計數器A為6,計數器B為8,則4個控制寄存器的控制字分別設置為R分頻器6200AOH,N分頻器200819H,功能寄存器003092H,初始化寄存器003093H。當按鍵發出指令,要求升高或降低本振輸出頻率時,改變計數器A和B的值,并重新加載ADF411l的控制寄存器,最終實現本振輸出頻率的改變。

電子發燒友App

電子發燒友App

評論