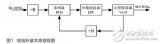

)、鎖相環頻率合成技術(PLL)、直接數字頻率合成技術(DDS)、混合頻率合成技術四種實現方式,其中鎖相環頻率合成器是射頻電路中最常使用的一種結構,相比于其他幾種結構,PLL結構能夠在有限的功耗限制下合成高性能的載波信號。

2015-10-17 11:24:00 1656

1656

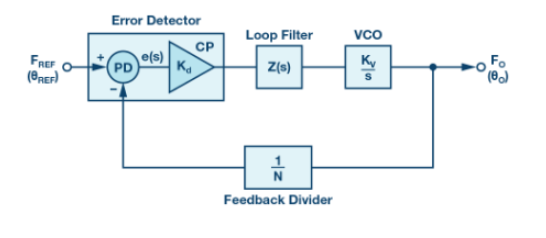

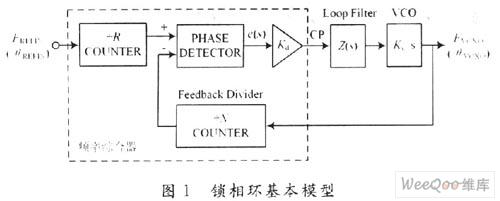

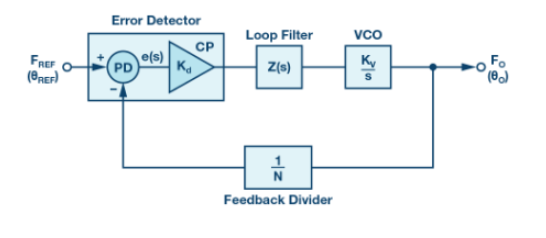

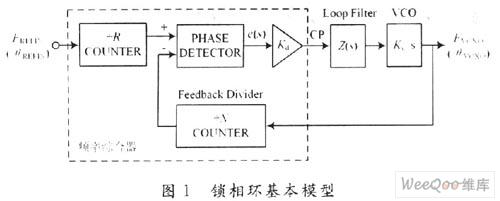

。當比較結果處于穩態,即輸出頻率和相位與誤差檢測器的輸入頻率和相位匹配時,我們說PLL被鎖定。就本文而言,我們僅考慮ADI ADF4xxx系列PLL所實現的經典數字PLL架構。 該電路的第一個基本元件是鑒頻鑒相器(PFD)。PFD將輸入到REFIN的頻率和相位與反饋到RFIN的頻率和相位進

2021-03-02 16:34:02 3806

3806

ADF4111 - 400 MHz to 6 GHz Broadband Quadrature Modulator - Analog Devices

2022-11-04 17:22:44

ADF4111BCP - RF PLL Frequency Synthesizers - Analog Devices

2022-11-04 17:22:44

最近在調試鎖相芯片ADF4001,問題是這樣的:我計劃用鎖相調頻,設置載波頻率為34.7Mhz,參考頻率REFin是用的是有源晶振24Mhz,鑒相頻率設為100kHZ,調試好VCO后發現根本無法鎖相

2019-03-12 14:43:36

;無線電臺基站。 一般說明 ADF4108頻率合成器可用于實現上轉換和下轉換部分的本地振蕩器無線接收器和發射器。它由低噪音組成數字鑒頻器,精密電荷泵可編程參考分壓器,可編程A和B計數器,以及一個雙模

2020-07-17 15:17:58

想用ADF4110做鎖相環,并實現雷達傳感器的LFMCW,雷達傳感器自帶VCO。采用1MHZ晶振作為參考頻率REFIN,雷達反饋信號為分頻后信號,范圍是2~3Mhz方波,作為RFINA的輸入。但是

2018-08-24 11:28:57

(小數 N 模式),可實現更高的相位噪聲和雜散性能。使用 49 位分值時,可變模數 Δ-Σ 調制器可以實現極精細的分辨率。ADF41513 可用作整數 N 鎖相環 (PLL) 或小數 N PLL,可使

2019-07-09 13:46:26

求一ADF5355_鎖相環相關資料,最好中文版,詳細點

2017-03-06 23:32:13

數字可調恒壓源是用什么方式實現多點電壓/電流校準?請具體點,是寫一個軟件。還是開發另外一套校準硬件設備?

2016-01-12 21:02:40

mA,頻率范圍為0~1 MHz.詳細講述了該調頻電流源實現的重要技術以及相應的公式推導.對所設計的調頻電流源電路的性能進行了仿真,仿真結果表明,其輸出頻率0~1 MHz.幅度0~20 mA內可調,符合

2018-11-29 17:06:14

隨著現代電子技術的發展,具有高穩定性和準確度的頻率源已經成為通信、雷達、儀器儀表、高速計算機及導航系統的主要組成部分。高性能的頻率源可通過頻率合成技術獲得。隨著大規模集成電路的發展,鎖相式頻率合成

2019-06-20 06:24:14

頻率合成技術實現的頻率源已經在雷達、通信、電子等領域得到了廣泛應用。 本文以GPS信號源設計為參考,介紹ADI公司的頻率合成器ADF4360-4在GPS信號源設計中的典型應用。

2019-06-25 07:07:32

1.AD4111與主機通訊的SCLK頻率怎么設置?

2.AD4111的內部校準和系統校準有什么區別,一般選哪個,是否一定需要校準?

3.CHANNEL REGISTER中的INPUT[9:0]的輸入

2023-12-07 06:22:49

EVAL-ADF4351EB1Z,該板設計用于允許用戶評估ADF4351頻率合成器的性能,以實現鎖相環(PLL)。它顯示了該板,其中包含ADF4351集成合成器和VCO,用于輸出信號的SMA連接器

2019-03-01 08:03:03

由鎖相環構成的間接式頻率合成器在無線通信領域發揮著非常重要的作用。通常采用鎖相頻率合成器的輸出信號來作為無線接收機中的本振信號,以使直接頻率調制器、頻率解調器能夠從輸入信號中再生載波。如果用MB1504/MAX2620的話怎么能夠實現鎖相時鐘頻率源?

2021-04-14 06:47:07

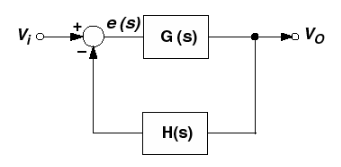

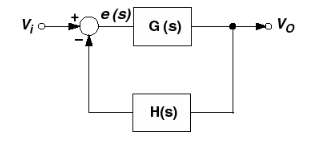

頻域中工作的負反饋控制環路。當比較結果處于穩態,即輸出頻率和相位與誤差檢測器的輸入頻率和相位匹配時,我們說PLL被鎖定。就本文而言,我們僅考慮ADI公司ADF4xxx系列PLL所實現的經典數字PLL架構

2019-10-02 08:30:00

。圖2中有一個在頻域中工作的負反饋控制環路。當比較結果處于穩態,即輸出頻率和相位與誤差檢測器的輸入頻率和相位匹配時,我們說PLL被鎖定。就本文而言,我們僅考慮ADI公司ADF4xxx系列PLL所實現

2019-01-28 16:02:54

介紹了鎖相環路的基本原理,分析了集成鎖相環芯片ADF4106的工作特性,給出了集成鎖相環芯片ADF4106的一個應用實例,為高頻頻率合成器的設計提供了很好的思路。 關鍵詞:ADF4106,鎖相環,頻率合成器,環路濾波器

2019-07-04 07:01:10

求大嬸指導ADF4111頻率合成器的編程啊。明明只有四個寄存器卻要編寫那么多控制字。新人暈了{:10:}

2014-04-27 14:46:03

的頻率切換。 頻率合成技術是利用參考頻率源來產生具有一系列離散的、高準確度、高穩定度頻率信號的一項技術。鎖相式頻率合成器是利用鎖相環(PLL)將壓控振蕩器(VCO)的頻率鎖定在某一個頻率點上,由壓控振蕩器

2019-06-25 05:00:05

ADF4351鎖相環介紹及相關硬件設計ADF4351是ADI公司推出的一款集成VCO的鎖相環芯片。其輸出頻率范圍可配置為35MHZ到4400MHZ,這取決于參考頻率和寄存器配置。其內部包括整數N

2022-01-11 07:28:51

(DS)、鎖相環頻率合成技術(PLL)、直接數字頻率合成技術(DDS)、混合頻率合成技術四種實現方式,其中鎖相環頻率合成器是射頻電路中最常使用的一種結構,相比于其他幾種結構,PLL結構能夠在有限的功耗限制

2018-09-06 14:32:13

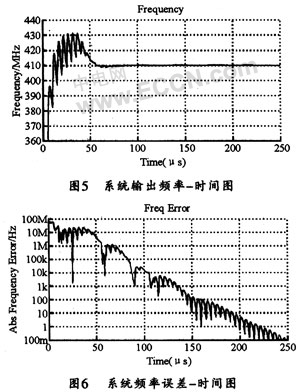

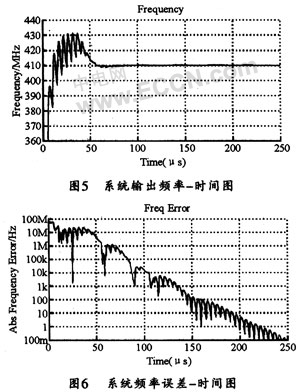

摘要:ADI提供了一套FMCW民用雷達方案,其中推薦的鎖相環就是ADF4159。本文著重于采用ADISimPLL用于輔助設計環路濾波器、產生調頻波的仿真。(據悉ADISimPLL并不是基于仿真器計算

2019-02-18 13:27:35

如何用集成電路MAX2620和集總LC元件構成窄帶VCO電路模塊,然后同集成鎖相頻率合成器芯片MB1504一起構成鎖相環式低噪聲、高穩定性的鎖相頻率源電路?

2021-04-07 06:33:42

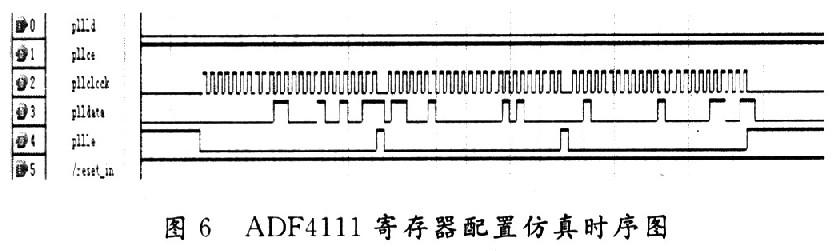

鎖相環是什么工作原理?如何采用FPGA與頻率綜合器ADF4111相結合的方法實現數字鎖相式頻率源的設計?

2021-04-14 07:00:20

全數字鎖相環由那幾部分組成?數字鎖相環的原理是什么?如何采用VHDL實現全數字鎖相環電路的設計?

2021-05-07 06:14:44

很多開關穩壓器都具有外部頻率可調(在外電路串接一個電阻即可調頻),或者直接給一個同步時鐘來設置自己想要的工作頻率,它的內部電路設計原理是什么樣的呢?跟普通的振蕩器有什么不一樣的地方?它是通過什么電路來實現這個可調或者同步的功能呢?

2017-05-08 10:34:09

到限制。而鎖相頻率合成主要是通過晶體振蕩器提供的標準頻率,在給定的頻率范圍內產生與該晶體振蕩器穩定度相同的大量離散頻率信號。 本文介紹用集成電路MAX2620和集總LC元件構成窄帶VCO電路模塊,然后同集成鎖相頻率合成器芯片MB1504一起構成鎖相環式低噪聲、高穩定性的鎖相頻率源電路的設計方法。

2019-07-09 08:12:36

最近使用ADF5356 | 小數N分頻鎖相環 (PLL)實現信號源,FPGA控話制SPI,始終不能鎖定,初始化配置899MHZ沒問題,但是更改N,F值不能鎖定,按照手冊更改各種參數和配置順序,硬是

2018-11-18 20:47:39

或射頻信號提供本振。頻率合成的基本方法有三種:直接頻率合成、鎖相式頻率合成以及直接數字頻率合成。鎖相式頻率綜合器是現今應用最為廣泛的一種頻率綜合器,它具有輸出頻率范圍大,雜散抑制特性好的特點。

2019-08-16 06:27:57

或射頻信號提供本振。頻率合成的基本方法有三種:直接頻率合成、鎖相式頻率合成以及直接數字頻率合成。鎖相式頻率綜合器是現今應用最為廣泛的一種頻率綜合器,它具有輸出頻率范圍大,雜散抑制特性好的特點。

2019-08-19 06:40:49

文末下載完整資料????????????????數字式調頻收音機設計摘要:本文利用數字鎖相頻率合成技術構成收音機的電調諧部分,完成收音機的調臺、選臺、搜索與存儲等功能。本文著重介紹了SONY公司生產

2021-12-07 08:50:47

數字鎖相環頻率合成系統的工作原理CPU控制數字鎖相環頻率合成系統FPGA實現

2021-04-09 06:20:37

想要實現一個900MHz左右的鎖相頻率源,不知道用什么芯片好,上網找了一些,但沒用過不知道是否好用,求推薦~!

2013-04-16 13:26:18

EV-ADF41020EB1Z,用于ADF41020 PLL頻率合成器評估板的評估板。評估用于鎖相環(PLL)的ADF41020頻率合成器。它包含ADF41020合成器,100 MHz TCXO,電源,USB接口和RF輸出。板載有一個有源環路濾波器和一個13 GHz VCO

2019-02-28 07:23:02

評估板EVAL-ADF4152HVEB1Z旨在讓用戶評估ADF4152HV頻率合成器的性能,以實現鎖相環(PLL)。該板包含ADF4152HV合成器,環路濾波器,1GHz至2GHz倍頻程的壓控振蕩器

2019-03-01 10:17:42

EV-ADF4153ASD1Z評估板旨在讓用戶評估ADF4153A頻率合成器的性能,以實現鎖相環(PLL)。它顯示了包含ADF4153A合成器的板,用于RF輸出信號的邊緣安裝SMA連接器,電源連接器

2019-02-27 11:21:47

的頻率是由ADF4159設置還是由ADF5901設置?我們的理解是:ADF5901先設置一個初步的頻率例如為24GHZ,然后再設置ADF4159產生連續的調頻三角波,ADF4159輸出的三角波控制ADF5901的輸出頻率。不知道這樣理解可以么?

2018-08-13 06:39:56

工程師您好:ADF4351內部集成VCO振蕩器,如果結合外部環路濾波器和外部參考時鐘頻率能構成數字鎖相環嗎?如果不能是不是因為ADF4351內部沒有鑒相器,如果我想做數字鎖相環還要和ADF4002合用嗎?能實現位同步嗎?期待您們的答復!

2018-09-14 14:23:29

您好,我們目前在做一個調頻連續波的雷達,DDS輸出50~60MHz,使用ADI的鎖相環ADF4108 96倍頻至4.8GHz~5.8GHz,掃頻周期4ms,點頻測試時鎖相環的相位噪聲還可

2018-08-16 07:18:19

我用信號源作為ADF4350的參考源,寄存器設置時以20M為參考頻率,鑒相器頻率為20M,環路帶寬設為100K,輸出頻率設為2G,信號源輸出20M時,ADF4350能夠鎖定,輸出頻率為2G,然后我

2018-10-25 09:19:11

文中在簡要敘述鎖相環的基本原理的基礎上,介紹了 ADF4218L 的主要特點及基于ADF4218L 鎖相頻率合成器硬件電路的設計和實現。在此基礎上討論了實際電路調試中應該注意的問

2009-08-13 09:59:45 41

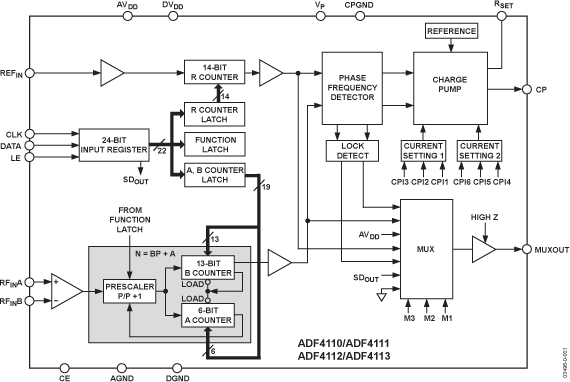

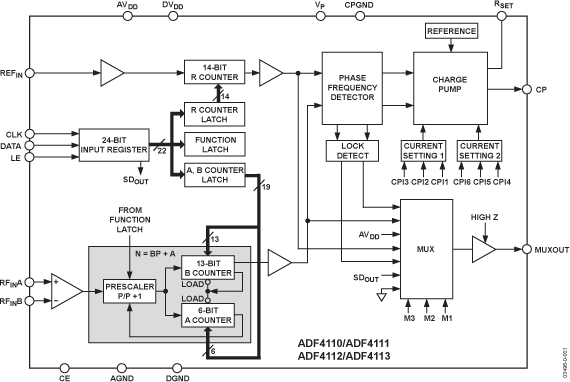

41 The ADF4110 family of frequency synthesizers can be used to implement local oscillators

2009-09-16 08:31:00 54

54 介紹了鎖相頻率合成器的基本原理,分析了高集成N分頻的鎖相頻率合成器ADF4360-4的工作特性,介紹了ADF4360-4在WLAN混頻電路中應用實例,并給出了設計方法、控制流程以及程序代碼

2010-12-11 15:57:28 22

22 鎖相環的研究和頻率合成一、實驗目的:1. 振蕩器(VCO)的V—f 特性的研究2. 對稱波鎖相環基本特性的研究3. 利用鎖相環實現頻率合成二、鎖相環原理:

2009-03-06 20:02:52 1939

1939

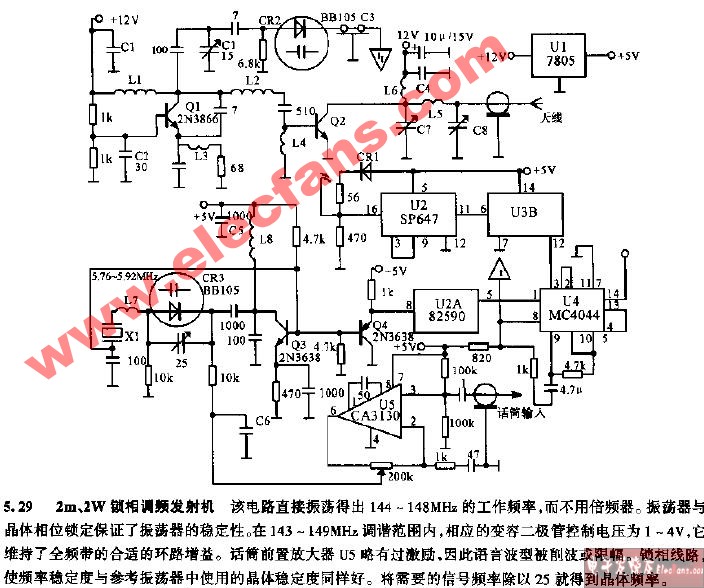

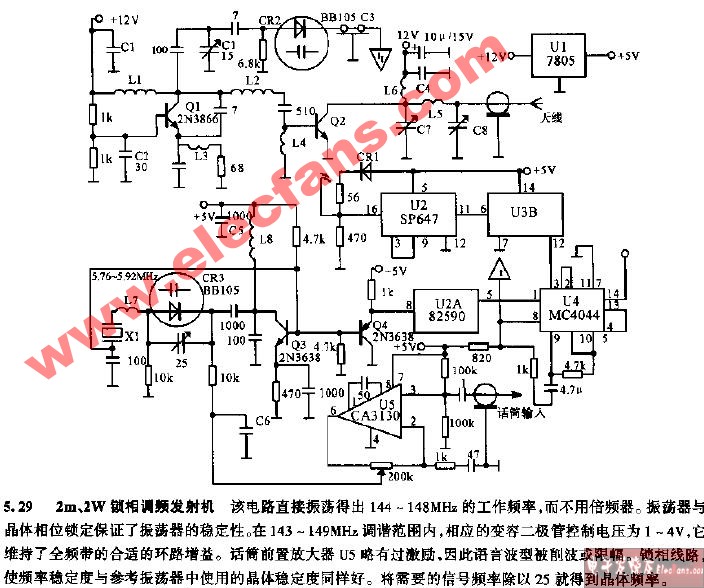

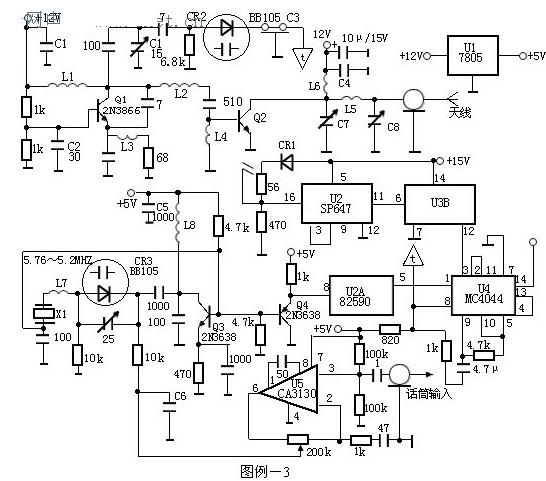

2m,2W鎖相調頻發射機

2009-03-15 13:31:28 1262

1262

介紹了鎖相環路的基本原理,分析了集成鎖相環芯片ADF4106的工作特性,給出了集成鎖相環芯片ADF4106的一個應用實例,為高頻頻率合成器的設計提供了很好的思路。???

2009-05-05 19:57:57 2585

2585

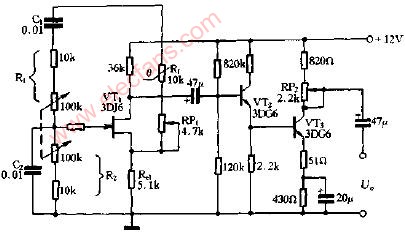

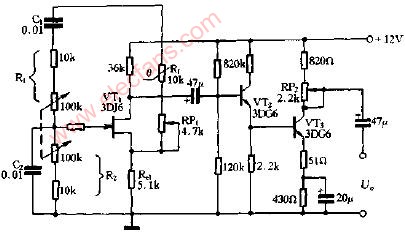

可調頻率的文氏電橋振蕩電路圖

2009-05-07 13:24:46 2771

2771

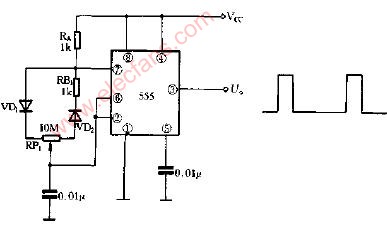

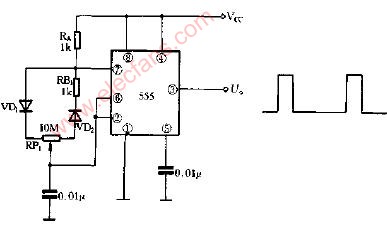

占空比可調頻率不變的多諧振蕩器電路圖

2009-05-08 14:58:53 5274

5274

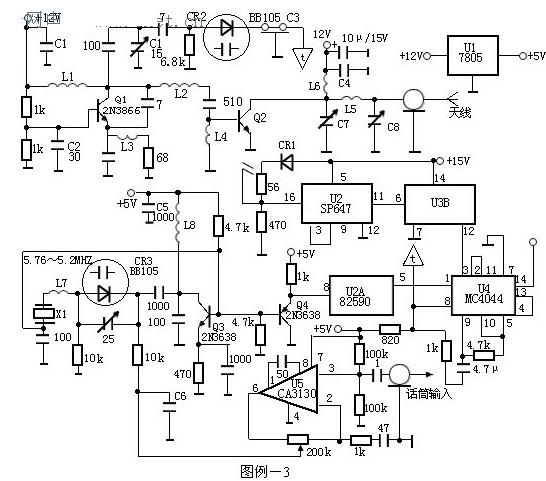

DMR終端鎖相調頻接收機設計

2004年,歐洲電信標準協會(ETSI)提出新型數字集群通信系統DMR(Digital Mobile Radio),DMR系統與TETRA和iDEN系統相比具有易于實現、成本低廉等優勢,已經

2009-12-05 18:02:15 1581

1581 2m,2w鎖相調頻發射機

2009-12-22 11:38:35 1764

1764

單片機控制的ADF4106鎖相頻率合成器設計

本文提出了一種基于單片機AT89C2051控制的、利用鎖相技術、以ADI公司生產的頻率合成器芯片AD4106為核心,來

2010-05-06 10:38:47 2982

2982

頻率合成器可以提供大量精確、穩定的頻率作為無線通信設備的本振信號。簡要介紹了鎖相環頻率合成器的基本原理,并利用整數N鎖相芯片ADF4112設計了一個寬波段的頻率合成器。討論

2011-05-03 18:20:24 101

101 本文介紹了一種通過快速改變鎖相環分頻器分頻比,來產生線性調頻信號的頻率綜合器,并對影響其掃描線性度的因素進行了分析。此方法擁有頻率精度高、易于調試以及線性度好等特

2011-06-20 09:58:54 4065

4065

運用數字鎖相頻率合成的思想,以ADI公司生產的數字分頻器和鑒相器ADF4113為核心,設計了頻率范圍在1.58 GHz一1.78 GHz的本振掃頻源。重點闡述了系統的硬件實現,包括系統設計方案、

2011-09-29 17:04:47 36

36 為得到性能優良、符合實際工程的鎖相環頻率合成器,提出了一種以ADI的仿真工具ADIsimPLL為基礎,運用ADS(Advanced Design System 2009)軟件的快速設計方法。采用此方法設計了頻率輸出為

2013-01-10 16:50:36 81

81 基于FPGA的數字鎖相環設計與實現技術論文

2015-10-30 10:38:35 9

9 Xilinx FPGA工程例子源碼:用FPGA實現數字鎖相環

2016-06-07 15:07:45 37

37 以數字鎖相環ADF4351和Xilinx公司的Spartan-6系FPGA為主要元件設計了一個合成頻率源。重點討論了ADF4351的工作原理、兩者之間的SPI通信過程、電路板的設計過程,并給出了關鍵

2017-11-15 11:27:20 32073

32073

公司的頻率綜合器ADF4111和Altera公司的FLEXlOKE系列FPGA實現頻率穩定,精度高,范圍為70~90 MHz,步進間隔1 MHz的數字鎖相式頻率源本振。

2019-02-06 09:20:00 1813

1813

電子發燒友網為你提供ADI(ti)ADF4111相關產品參數、數據手冊,更有ADF4111的引腳圖、接線圖、封裝手冊、中文資料、英文資料,ADF4111真值表,ADF4111管腳等資料,希望可以幫助到廣大的電子工程師們。

2019-02-22 15:20:34

STM32如何實現可調頻率、占空比的PWM波形,且可指定輸出脈沖個數?

2020-03-12 11:04:06 24012

24012 STM32F4_TIM輸出PWM波形(可調頻率、占空比)

2020-03-24 11:26:07 13069

13069 模塊提供5.4 GHz 的單音本振信號并且利用數控衰減器和放大器實現了輸出功率可調,同時也利用ADF5355 的鎖相環(PLL)和倍頻器為射頻模塊提供8.4~11.2 GHz 寬頻帶寬、步進為100 MHz 的可調頻本振信號,最終通過硬件電路的設計與調試,以及單片機(SCM)控制程序的編寫

2020-11-11 10:39:00 4

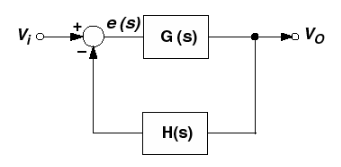

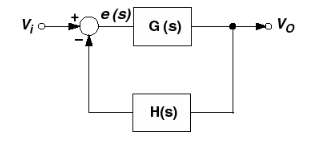

4 鎖相環路是一種反饋控制電路,簡稱鎖相環( PLL)。鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。因鎖相環可以實現輸出信號頻率對輸入信號頻率的自動跟蹤, 所以鎖相環通常

2020-08-06 17:58:25 24

24 本文檔的主要內容詳細介紹的是使用MC145170鎖相環實現調頻鎖相環收音機的PCB原理圖免費下載。

2020-11-02 17:15:00 77

77 UG-369:ADF4151鎖相環頻率合成器評估板

2021-04-19 20:14:47 6

6 UG-802:用于鎖相環的ADF5355頻率合成器評估

2021-04-25 12:23:05 3

3 UG-873:評估ADF4355-3小數/整數N鎖相環頻率合成器

2021-04-28 14:35:35 5

5 ADF4110/ADF4111/ADF4112/ADF4113:RF PLL頻率合成器數據表

2021-04-29 12:21:34 9

9 UG-804:評估ADF4355-2小數/整數N鎖相環頻率合成器

2021-05-10 08:26:33 8

8 UG-383:用于鎖相環的ADF4159頻率合成器評估

2021-05-10 13:26:06 1

1 UG-485:ADF4153A小數N鎖相環頻率合成器評估板

2021-05-16 13:22:43 8

8 UG-1087:用于鎖相環的ADF5356頻率合成器評估

2021-05-17 09:38:07 4

4 ADF4217:雙射頻鎖相環頻率合成器過時數據表

2021-05-17 11:55:55 2

2 用鎖相環實現超快頻率切換

2021-05-18 20:29:01 9

9 LTC3805-5:可調頻率電流模式反激/升壓/SEPIC DC/DC控制器數據表

2021-05-23 20:30:21 6

6 UG-389:ADF4xxx鎖相環頻率合成器的USB轉并行轉接板

2021-05-24 11:46:02 6

6 UG-686:ADF4155鎖相環頻率合成器評估板

2021-05-25 16:46:51 4

4 ADF4150HV鎖相環頻率合成器UG-406評估板

2021-06-03 11:16:33 7

7 電子發燒友網為你提供ADI(ti)EVAL-ADF4111相關產品參數、數據手冊,更有EVAL-ADF4111的引腳圖、接線圖、封裝手冊、中文資料、英文資料,EVAL-ADF4111真值表,EVAL-ADF4111管腳等資料,希望可以幫助到廣大的電子工程師們。

2021-07-25 09:00:02

文末下載完整資料????????????????數字式調頻收音機設計摘要:本文利用數字鎖相頻率合成技術構成收音機的電調諧部分,完成收音機的調臺、選臺、搜索與存儲等功能。本文著重介紹了SONY公司生產

2021-11-24 13:36:10 39

39 ADF435x微波寬帶頻率合成器搭配外部環路濾波器和外部基準頻率使用時,可實現小數N分頻或整數N分頻鎖相環 (PLL) 頻率合成器。ADF435x使用一系列分頻器,可以在35MHz到 6800MHz范圍內運行。

2022-07-23 09:30:42 2

2 鎖相環是一種反饋系統,結合了壓控振蕩器和相位比較器,其連接方式使振蕩器頻率(或相位)精確跟蹤施加的頻率或相位調制信號的頻率(或相位)。例如,鎖相環可用于從固定的低頻信號生成穩定的輸出頻率信號。第一個

2023-01-30 09:50:10 1232

1232

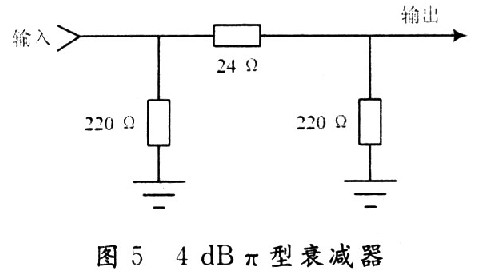

第一部分將重點介紹有關PLL的基本概念,同時描述基本PLL 架構和工作原理,另外,我們還將舉例說明PLL在通信系統 中的用途。最后,我們將展示一種運用ADF4111頻率合成器 和VCO190-902T電壓控制振蕩器的實用PLL電路。

2023-06-17 14:47:10 666

666

電子發燒友網站提供《基于ADF4111的鎖相環頻率合成器設計.pdf》資料免費下載

2023-10-20 14:45:29 0

0 數字鎖相環(DigitalPhase-LockedLoop,簡稱DPLL)是一種基于反饋控制的技術,用于實現精確的時序控制和相位同步。通過相位比較、頻率差計算、頻率控制、濾波和循環控制,它能夠完成

2024-01-02 17:20:25 701

701

電子發燒友App

電子發燒友App

評論