您的位置:電子發燒友網 > 電子技術應用 > 行業新聞 > 新品快訊 >

賽靈思推出采用堆疊硅片互聯技術的世界最大容量FPGA:Virtex-7 2000T

2011年10月26日 14:31 來源:電子發燒友網 作者:葉子 我要評論(0)

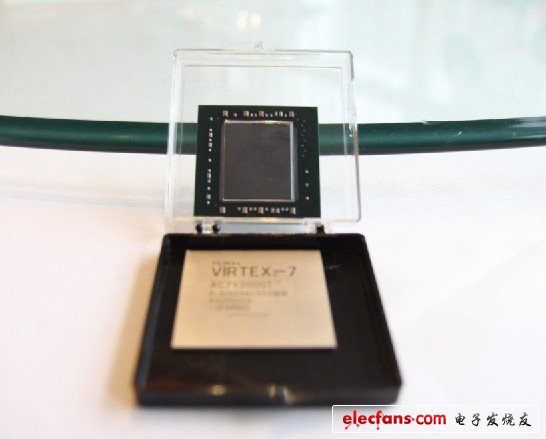

賽靈思已向客戶推出世界最大容量FPGA:Virtex-7 2000T。這款包含68億個晶體管的FPGA具有1954560個邏輯單元,容量相當于市場同類最大28nm FPGA的兩倍。這是賽靈思采用臺積電(TSMC)28nm HPL工藝推出的第三款FPGA,更重要的是,這也是世界第一個采用堆疊硅片互聯(SSI)技術的商用FPGA。

賽靈思可編程平臺開發全球高級副總裁Victor Peng指出:“Virtex-7 2000T FPGA是賽靈思創新和業界合作史傷的一個重大里程碑。如果沒有堆疊硅片互聯(SSI)技術,至少要等到下一代工藝技術,才有可能在單個FPGA中實現如此大的晶體管容量。就通常新一代產品的推出而言,SSI至少提前一年講我們的最大型28nm期間交付給了客戶。這對ASIC和ASSP仿真和原型而言尤其重要。”

傳統上,FPGA廠商習慣于采用最新芯片工藝技術來實現他們的新架構,充分發揮摩爾定律的作用,這樣晶體管的數量每22個月就能隨最新芯片工藝技術的推出而翻一番。過去20年,FPGA廠商一直遵循摩爾定律的發展,不斷推出新的FPGA,實現器件容量的倍增。

Vertex-7 2000T的推出,標志著賽靈思取得了一個重大成就,也標志著賽靈思向半導體產業的3D IC邁進了一大步。ChandraseKaram指出,該產品的真正價值在于開啟了用戶創新之門,為苦心尋找最大容量器件的客戶帶來了新的設計能力。他說:“對那些希望加速產品開發,為軟件開發人員提供芯片仿真功能,或者期待將多個芯片整合到單個器件中,以及那些發現其設計不能采用ASIC的客戶而言,他們都將從這一了不起的技術中大受其益。通過采用SSI技術,賽靈思現在就把下一代才能提供的超大容量FPGA,交到設計人員手中。”

大型單芯片的制造挑戰。

ARM 設計技術和自動化副總裁John Goodenough指出:“ARM公司很高興與賽靈思合作,在我們的驗證基礎架構中部署業界領先的Virtex-7 2000T器件。這一新型器件支持一種靈活而有針對性的模擬仿真架構,能大幅提升容量,使我們能夠針對ARM的下一代處理器更加輕松地進行全面的系統驗證與確認。”

Virtex-7 2000T器件還為設備制造商提供了一個集成的平臺,能幫助他們在提升性能和功能的同時降低功耗。由于消除了電路板上不同IC 間的I/O接口,系統的整體功耗得以顯著降低。同時,因為電路板上需要的IC 器件數量減少,客戶能降低材料清單成本、測試和開發成本。此外,由于芯片在硅中介層上并排放置,SSI 技術能夠避免多個芯片堆疊造成的功耗和可靠性問題。中介層在每個芯片間提供10,000多個高速互聯,可支持各種應用所需要的高性能集成。

Virtex-7 2000T FPGA為客戶提供了通常只有大容量ASIC 才具備的容量、性能和功耗水平,更增加了可重編程的優勢。由于越來越多的系統和市場對ASIC 的開發成本感到難以承受,Virtex-7 2000T FPGA為那些面臨ASIC 修改風險和超過5,000萬美元的28nm 定制ICNRE成本的設計,提供了一個獨特的、可擴展的替代解決方案。

賽靈思所有28nm 器件(Artix™-7、Kintex™-7、Virtex®-7 FPGA和Zynq™-7000 EPP)均采用統一架構,能夠在同一系列的不同產品間以及不同系列的產品間支持設計和IP 重用。這些器件均采用臺積電的28nm HPL(低功耗高介電層金屬閘技術)工藝制造,這樣制造出來的FPGA 靜態功耗比同類競爭產品降低一半。隨著器件容量的增大,靜態功耗降低的意義越發顯著。Virtex-7 2000T相對于采用多個FPGA實現的設計方案而言,功耗更低,其中28nm HPL起到了關鍵作用。