您的位置:電子發(fā)燒友網(wǎng) > 電子技術(shù)應(yīng)用 > 嵌入式技術(shù) > FPGA/ASIC技術(shù) >

賽靈思Virtex-7 2000T FPGA和堆疊硅片互聯(lián)(SSI)技術(shù)常見問題解答

2011年10月26日 14:35 來源:電子發(fā)燒友網(wǎng) 作者:葉子 我要評論(0)

1. 賽靈思今天宣布推出什么產(chǎn)品?

賽靈思采用了稱之為“堆疊硅片互聯(lián)技術(shù)”的 3D 封裝方法,該技術(shù)采用無源芯片中介層、微凸塊和硅通孔 (TSV)技術(shù),實現(xiàn)了多芯片可編程平臺。對于那些需要高密度晶體管和邏輯、以及需要極大的處理能力和帶寬性能的市場應(yīng)用而言,這些28nm平臺和單芯片方法相比,將提供更大的容量,更豐富的資源,并顯著降低功耗。

2. 賽靈思所謂的“超越摩爾定律”是什么意思?

到目前為止,F(xiàn)PGA 的所有工藝節(jié)點都遵循摩爾定律的發(fā)展,邏輯容量提高一倍,則成本降低一半。遺憾的是,僅僅依靠摩爾定律的發(fā)展速度,已不能滿足市場對可控功耗范圍內(nèi)實現(xiàn)更多資源以及更高代工廠良率的無止境的需求。堆疊硅片互聯(lián)技術(shù)使賽靈思能夠推出一款可有效解決上述難題的可編程解決方案。

3. 為什么客戶不能簡單地把兩個或更多 FPGA 連接起來實現(xiàn)大規(guī)模設(shè)計?

這種簡單連接的方法有三大缺點:一是可用 I/O 數(shù)量有限,不足以連接用以供分區(qū)設(shè)計中不同 FPGA 間信號傳輸?shù)膹?fù)雜網(wǎng)絡(luò),同時也難以連接 FPGA 到系統(tǒng)其它器件;二是 FPGA 間傳輸信號的時延限制了性能;三是在多個 FPGA 之間用標(biāo)準(zhǔn)器件 I/O 創(chuàng)建邏輯連接會引起不必要的功耗。

4. 使用堆疊硅片互聯(lián)技術(shù)時有沒有特殊的熱管理要求?

沒有。由于中介層為無源的,因此除了FPGA 芯片消耗熱量外,不存在其它散熱問題。因此,如果這么大的單片器件可以制造, 采用堆疊硅片互聯(lián)技術(shù)的 FPGA 產(chǎn)品就相當(dāng)于一個單芯片。

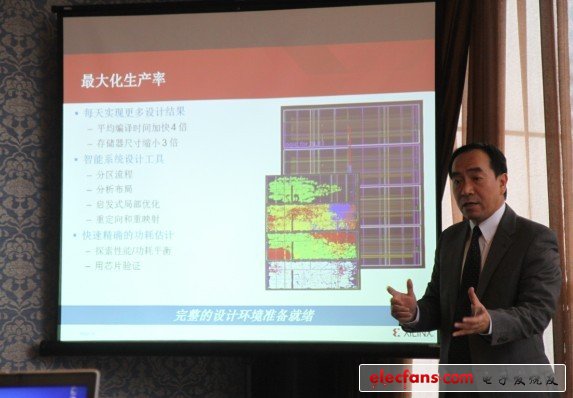

賽靈思公司全球高級副總裁,亞太區(qū)執(zhí)行總裁Vincent Tong講解Virtex-7 2000T產(chǎn)品優(yōu)勢

5. 堆疊硅片互聯(lián)技術(shù)是否可靠?

是的,很可靠。由于較薄的硅中介層可有效減弱內(nèi)部堆積的應(yīng)力,一般說來堆疊硅片互聯(lián)技術(shù)封裝架構(gòu)的內(nèi)部應(yīng)力低于同等尺寸的單個倒裝 BGA 封裝,這就降低了封裝的最大塑性應(yīng)變,熱機械性能也隨之得以提升。

6. 堆疊硅片互聯(lián)技術(shù)生產(chǎn)的 FPGA主要針對那些人群?

任何需要超過現(xiàn)有邏輯密度水平的高密度 FPGA 的客戶都能受益于采用堆疊硅片互聯(lián)技術(shù)的 FPGA 產(chǎn)品。通信、醫(yī)療、測試和測量、航空航天和國防、高性能計算以及ASIC 原型設(shè)計(仿真)等市場領(lǐng)域的客戶,當(dāng)他們希望使用FPGA來部署其下一代的、最苛刻的應(yīng)用時, 都將有機會受益于早期供應(yīng)的資源最豐富的FPGA器件。由于無需在相鄰 FPGA 間通過 I/O 接口和 PCB 走線來驅(qū)動芯片,因此此前在系統(tǒng)中使用多個 FPGA 的設(shè)計人員, 將享用到FPGA芯片之間更高的帶寬、更低的功耗、以及更快速的連接方式。

7. 就采用堆疊硅片互聯(lián)技術(shù)的產(chǎn)品而言,賽靈思有哪些設(shè)計指南?

賽靈思的 ISE® 設(shè)計套件將提供新的功能,助力基于堆疊硅片互聯(lián)技術(shù)的 FPGA 產(chǎn)品的設(shè)計工作。其中有設(shè)計規(guī)則檢查(DRC)和軟件信息可引導(dǎo)用戶實現(xiàn) FPGA 芯片間的邏輯布局布線。此外,PlanAhead 和 FPGA Editor功能增強了基于堆疊硅片互聯(lián)技術(shù)的 FPGA 器件的圖示效果,有助于開展互動設(shè)計布局規(guī)劃、分析及調(diào)試。與此同時,我們也正在編寫并推出可以為用戶提供詳細(xì)的最佳設(shè)計實踐指南的應(yīng)用手冊。

8. 客戶必須進(jìn)行設(shè)計分區(qū)嗎?軟件能否直接為他們進(jìn)行設(shè)計分區(qū)?

軟件可自動將設(shè)計分配到 FPGA 芯片中,無需任何用戶干預(yù)。如果需要,客戶可在特定 FPGA 芯片中進(jìn)行邏輯布局規(guī)劃。在沒有任何此類約束的情況下,軟件工具可讓算法智能地在 FPGA 芯片內(nèi)放置相關(guān)邏輯,并遵循芯片間和芯片內(nèi)的連接和時序規(guī)則。

9. 哪些產(chǎn)品將使用堆疊硅片互聯(lián)技術(shù)?

Virtex-7 2000T 器件是 Virtex-7 系列中最大型的產(chǎn)品,容量高達(dá) 200 萬個邏輯單元,并采用 36 個 10.3 Gbps收發(fā)器,它將是首款采用該技術(shù)的產(chǎn)品。首批產(chǎn)品預(yù)計將于 2011 年下半年推出。

10. 賽靈思的 7 系列產(chǎn)品是什么?

2010 年 6 月宣布推出的新型 28nm Artix-7、Kintex-7 和 Virtex-7 系列產(chǎn)品將功率、性能/容量和性價比等方面的突破性創(chuàng)新技術(shù)與前所未有的高可擴展性和生產(chǎn)率完美結(jié)合在一起,大大加強了賽靈思目標(biāo)設(shè)計平臺的戰(zhàn)略優(yōu)勢,從而使更廣闊的用戶群體、終端市場和應(yīng)用都能更方便地應(yīng)用可編程邏輯。所有的 7 系列 FPGA 產(chǎn)品均采用基于 28nm 工藝技術(shù)實施的統(tǒng)一架構(gòu),專門針對低功耗高性能的融合進(jìn)行了精心優(yōu)化。這種獨特的融合不僅使總功耗銳降50%,性價比和系統(tǒng)性能雙雙提升 2 倍,同時也是全球首款集成了 200 萬個邏輯單元的 FPGA(與前代產(chǎn)品相比,容量提升了 2.5 倍)。因此,設(shè)計人員現(xiàn)在能夠輕松滿足應(yīng)用擴展需求,讓 28nm 產(chǎn)品系列支持各種系統(tǒng)性能、容量和成本要求,同時不超出功耗預(yù)算。

11. 為什么ASIC 原型和模擬仿真是Vitex-7 2000T 器件的重要目標(biāo)市場?

就ASIC 原型和模擬仿真而言,客戶希望盡快獲得最新型FPGA。由于軟件開發(fā)在復(fù)雜系統(tǒng)開發(fā)周期中常常要占用大量的時間,因此要是等ASIC 完成后才開始進(jìn)行軟件開發(fā),會耽誤整個系統(tǒng)的開發(fā)進(jìn)度,有時甚至要耽誤長達(dá)2 年的時間。有了Virtex-7 2000T 原型或模擬仿真平臺,SoC 軟件開發(fā)就能大大提前,開發(fā)人員也不必再苦等ASIC 的完成。

12. Virtex-7 2000T器件是如何支持系統(tǒng)集成商的?

在提高下一代系統(tǒng)性能和功能的同時降低功耗,這是設(shè)備制造商面臨的共同挑戰(zhàn)。要想實現(xiàn)上述目標(biāo),一種途徑就是通過系統(tǒng)集成,減少板上不同IC 間的I/O 接口數(shù)量,從而降低功耗。這是因為I/O 接口數(shù)量以及I/O 的性能與功耗成正比。設(shè)計性能越高,系統(tǒng)中IC 數(shù)量越多,功耗也就越大。此外還要注意,設(shè)計中使用的IC 數(shù)量增多,在不同器件間進(jìn)行設(shè)計分區(qū)的難度也會加大,這也會延長開發(fā)周期,提高測試成本,而采用Virtex-7 2000T 器件則能避免上述問題。

對于那些之前在系統(tǒng)中采用多個FPGA的通信、醫(yī)療、測試測量、航空航天與軍用以及高性能計算等領(lǐng)域的設(shè)計人員來說,Virtex-7 2000T將使其無需借助并行或者串行I/O, 或者通過片外的PCB連線與相鄰的FPGA 互聯(lián),即可充分享受到FPGA芯片內(nèi)高帶寬、低時延、低功耗互聯(lián)機制的優(yōu)勢。

標(biāo)簽:FPGA(5365)SSI(95)堆疊硅片互聯(lián)(5)