您的位置:電子發燒友網 > 電子技術應用 > 測量儀表 > 設計測試 >

通用電路板自動測試系統的設計與實現(2)

2011年10月25日 17:21 來源:本站整理 作者:秩名 我要評論(0)

2 系統詳細設計

2.1 針床設計

針床是電路板測試系統的重要部件,是電路板信號導出的平臺。針床的通用性較差,一般是每種電路板對應一個特定的針床,這使系統的通用性受到很大的限制。為使針床具有一定的通用性,本系統中對針床的相關部件進行了一些改進:

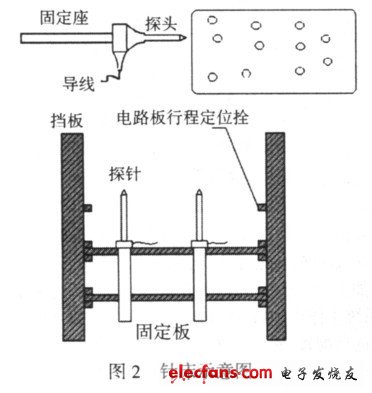

(1)探針設計。探針見圖2 a。本探針是以目前市場上的探針為基礎、自行設計的內含彈簧的探針,易于固定,信號導出方便:

探針的一端為探頭,是與電路板接觸,并導出信號的部分;另一端是固定座,是絕緣體,中空,內含彈簧,使探頭能夠伸縮;中間為信號的導出端子。為減少各個信號間的干擾,導線均采用屏蔽線。為適應不同信號要求,按粗細和允許的信號帶寬要求探針分為多種型號,使用時根據需要對探針型號進行選擇。

(2)探針的固定:在本系統的針床上,探針的固定是采用兩塊相同的探針固定板和4 塊擋板組成,固定板和探針的固定示意圖見圖2 b 和圖2c:固定板的大小與待測板相同,板上固定孔位置需根據電路板的技術文件來確定,孔的大小需根據選取探針的型號來決定。擋板可以在整個針床的底座上進行移動調整,以適應不同尺寸電路板的固定要求;擋板的寬度,前后兩個為233 mm,左右兩個為73 mm。

2.2 信號采集

電路板上輸出的待測信號主要有三類:電源信號、脈沖數字信號、電平變換信號。此外還有一些頻率較高的模擬信號,如音視頻信號,此類信號一般不作為關鍵測試信號,若需測試時可按高頻信號進行采集。其中電源信號和電平變換信號均可視為直流信號來采集,用AD7864 完成采集。而脈沖數字信號的頻率較高,動輒就幾十兆赫茲甚至上百兆赫茲,需要用高速的AD(本系統中用的是AT84AD331) 來進行采集,并且需要對頻率進行測量。因此本系統信號采集分為低頻和高頻兩個部分,下面分別敘述:

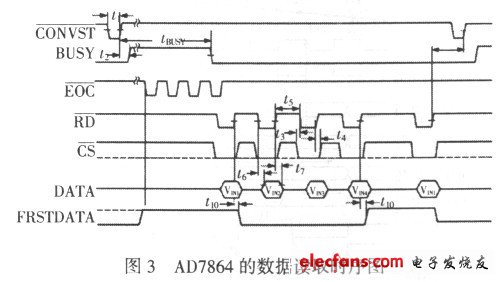

(1)低頻部分。本部分主要采集的是電源信號和電平變換信號,采用AD7864 作為采集芯片。AD7864 具有片內時鐘、讀寫允許邏輯、多種通道選擇方式以及內部精確的2。5 V 參考電壓,這使得其與高速處理器的接口變得非常簡單。AD7864 轉換后的數據讀取采用轉換后讀取數據的方式,其讀取時序見圖3。

采集到的數據為D3~D11 共12 位,需根據采集到的數據來計算電壓值,計算公式如下:

當D11 位為3 時,電壓為正值,計算公式為:

當D11 位為1 時,電壓為負值,計算公式為:

以上兩式中D 為讀取的12 位數據,FSR 為AD7864 的測量范圍,本例中為23 V(測量范圍為V)。

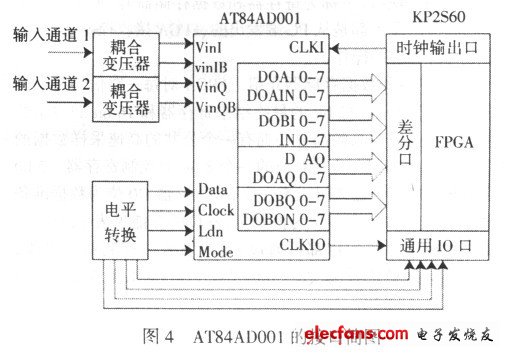

(2)高頻部分。主要是對脈沖數字信號的采集,包括頻率測量和信號采集兩個部分。脈沖數字信號的頻率是確定電路板是否工作正常的重要參數,因此確定脈沖信號的頻率是否正常是本測試系統的必要工作。本系統是將待測信號接入FPGA 與53MHz 的高精度時鐘同時開始計數,一段時間后,通過兩個信號的計數值來計算脈沖信號頻率的。信號采集是以AT84AD331 作為采集芯片。AT84AD331 與EP2S63 的連接見圖4。

AT84AD331 可以配置成I 路和Q 路單獨使用,此時可以同時采集兩路信號,最高采樣率為1 Gs/s;也可以配置成I 和Q 路的交錯采樣,此時只能采集1 路信號,等效采樣率為2 Gs/s,使用時可以根據需要對該芯片進行在線配置。FPGA 對AT84AD331數據讀取時序見圖5。

由于AT84AD331 輸入信號為差分信號,且信號峰峰值要求不超過533 mV。電路板上的待測信號都是單端的并且峰峰值一般在4 V~5 V 之間。本系統中采用了13∶1 的變壓器耦合輸入方式,可以完成單端信號到差分信號的轉換,并且使信號電壓滿足要求。

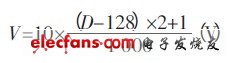

在FPGA 內部完成對LVDS 信號的讀取、組合、排序以及存儲等操作。一般情況下存儲的采樣點的值在1 333 以內,然后對這些采樣點的值進行計算,可以得到實際電壓值,計算公式如下:

本文導航

- 第 1 頁:通用電路板自動測試系統的設計與實現(1)

- 第 2 頁:系統詳細設計

- 第 3 頁:數據傳輸和控制協議