在Vivado中構(gòu)建AMD Versal可擴(kuò)展嵌入式平臺(tái)示例設(shè)計(jì)流程

為了應(yīng)對(duì)無(wú)線波束形成、大規(guī)模計(jì)算和機(jī)器學(xué)習(xí)推斷等新一代應(yīng)用需求的非線性增長(zhǎng),AMD 開(kāi)發(fā)了一項(xiàng)全新的....

AMD Versal系列CIPS IP核介紹

AMD自適應(yīng)計(jì)算加速平臺(tái)(ACAP)是一個(gè)完全軟件可編程資源集合,這些資源結(jié)合在一起構(gòu)成片上系統(tǒng) (....

Nand Flash接口定義解析 基于AMD FPGA的Nand Flash接口讀寫(xiě)實(shí)現(xiàn)

Nand Flash因其具有容量大、成本低、壽命長(zhǎng)的特點(diǎn),被廣泛的用作數(shù)據(jù)存儲(chǔ)的解決方案。然而Nan....

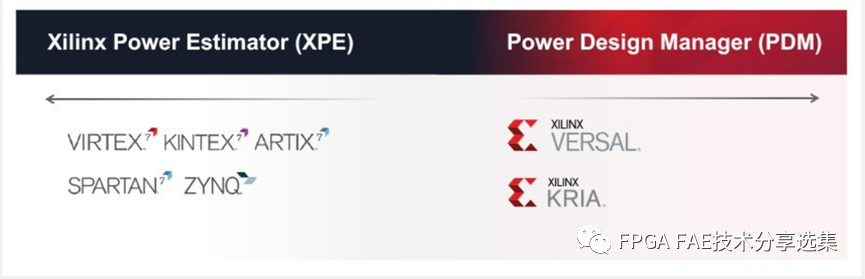

如何使用Power Design Manager(PDM)進(jìn)行功耗評(píng)估?

在基于FPGA和 SoC器件的產(chǎn)品設(shè)計(jì)過(guò)程中,從器件選擇到系統(tǒng)級(jí)電源設(shè)計(jì)、散熱設(shè)計(jì),電源功率估算對(duì)于....

基于AMD SOC的QT應(yīng)用程序開(kāi)發(fā)

基于AMD SOC的QT應(yīng)用程序開(kāi)發(fā)方法主要有兩種方式:一種方式是基于petalinux工程新建一個(gè)....

AMD Versal系列FPGA NoC介紹及實(shí)戰(zhàn)

NoC是相對(duì)于SoC的新一代片上互連技術(shù),從計(jì)算機(jī)發(fā)展的歷史可以看到NoC 必將是SoC 之后的下一....

基于AMD FPGA的PCIE DMA邏輯實(shí)現(xiàn)

AMD FPGA自帶PCIE硬核,實(shí)現(xiàn)了PCIE協(xié)議,把串行數(shù)據(jù)轉(zhuǎn)換為并行的用戶數(shù)據(jù),以UltraS....

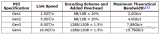

求一種基于AMD器件的EtherCAT從站方案

EtherCAT現(xiàn)場(chǎng)總線協(xié)議是由德國(guó)倍福公司在2003年提出的,該通訊協(xié)議拓?fù)浣Y(jié)構(gòu)十分靈活,數(shù)據(jù)傳輸....

基于IEEE802.1Q標(biāo)準(zhǔn)的TSN方案簡(jiǎn)介

隨著智能制造、工業(yè)物聯(lián)網(wǎng)、大數(shù)據(jù)的發(fā)展,許多工業(yè)自動(dòng)化應(yīng)用對(duì)于延遲和確定性的要求越來(lái)越嚴(yán)格。

FPGA ISP Bayer與常見(jiàn)顏色空間轉(zhuǎn)換介紹

FPGA實(shí)現(xiàn)ISP(Image Signal Processor)過(guò)程中,在圖像接收、處理、傳輸過(guò)程....

AMD-Xilinx FPGA功耗優(yōu)化設(shè)計(jì)簡(jiǎn)介

對(duì)于FPGA來(lái)說(shuō),設(shè)計(jì)人員可以充分利用其可編程能力以及相關(guān)的工具來(lái)準(zhǔn)確估算功耗,然后再通過(guò)優(yōu)化技術(shù)來(lái)....

利用Block Design加速設(shè)計(jì)

隨著FPGA的資源越來(lái)越大,設(shè)計(jì)的快速構(gòu)建、易修改、隨著版本可迭代的要求越來(lái)越高。好比在早期單片機(jī)時(shí)....