您的位置:電子發燒友網 > 電子技術應用 > 嵌入式技術 > FPGA/ASIC技術 >

龍芯處理器IP核的FPGA驗證平臺設計

2012年04月21日 15:22 來源:本站整理 作者:秩名 我要評論(0)

本文利用Altera公司的FPGA開發工具對皋于國產龍芯I號處理器IP核的SoC芯片進行ASIC流片前的系統驗證,全實時方式運行協同設計所產生的硬件代碼和軟件代碼,構建一個可獨立運行、可現場監測的驗證平臺。

1、基于龍芯I號處理器IP核SoC芯片

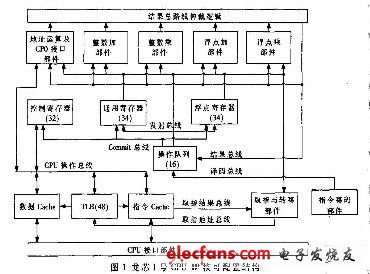

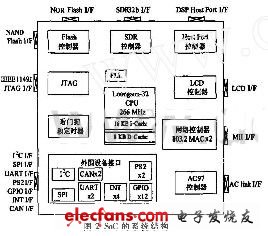

龍芯I號CPU IP核是兼顧通用及嵌人CPU特點的32位處理器內核,采用類MIPS Ⅲ指令集,具有7級流水線、32位整數單元和64位浮點單元;具有高度靈活的可配置性,方便集成的各種標準接口。圖1為龍芯I號CPU IP核可配置結構,用戶可根據自己的需求進行選擇配置,從而定制出最適合用戶應用的處理器結構。

圖1龍芯I號CPU IP核可配置結構

主要的可配置模塊包括:浮點部件、多媒體部件、內存管理、Cache、協處理器接口。浮點部件完全兼容MIPS的浮點指令集合,其相關的系統軟件完全符合ANSI/IEEE 754-1985二進制浮點運算標準。浮點部件主要包括浮點ALU部件和浮點乘法/除法部件,用戶可根據自己的實際應用選擇是否添加。媒體部件復用了MIPS浮點指令的Format域,并復用了浮點寄存器堆,媒體指令集基本對應了Intel SSE媒體指令集合的各種操作。圖2為基于龍芯I號CPU IP核的SoC系統架構。

圖2 SoC的系統結構

該SoC芯片支持通用MIPS32指令集,主頻可達266 MHz;內置MAC網絡,提供MII接口;存儲器接口,芯片同時支持SDRAM接口、NOR Flash/ROM和\AND Flash接口,并特置HPI接口可直接與Y0IP CODEC芯片相連;提供豐富的其他外設接凵支持,包括PC接口、UART串口、SP!接口、AC97等接口設備。提供豐富的GP10接口,能夠為“網絡+語音”以及工業控制應用提供高效的單芯片解決方案。

2 FPGA驗證平臺的設計

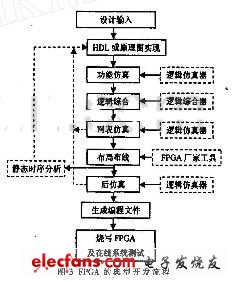

2.1 FPGA的開發流程

FPGA的典型開發流程如圖3所示。在圖3中,邏輯仿真器主要有Modelsim、Verilog_XL等,邏輯綜合器主要有LeonardoSpectrum、Synplify Pro、FPGA Ex~press/FPGA CompilerII等,FPGA廠家工具有Altera公司的Max+Plusll、Quartusll,Xilinx公司的Foundation ISE、Alliance等。設計輸人主要有原理圖輸人和HDL輸人兩種方式,絕大部分設計,FPGA和ASIC的工程師都使用HDL平臺。設計仿真主要包括功能仿真和網表仿真,設汁仿真需要RTL代碼或綜合后的HDL網表和驗證程序,有時候還需要測試數據,測試數據可能是代碼編譯后的二進制文件或使用專門的工具采集的數據。布局布線工具利用綜合生成的網表、調用模塊的網表,根據布局布線目標,把設計翻譯成原始的目標工藝,最后得到生成編程比特流所需的數據文件。布局布線一般需要的輸人輸出與調用關系如圖4所示。布局布線目標包括所使用的FPGA具體型號等,約束條件包括管腳位置、管腳電平邏輯(LVTIL、LCMOS等)需要達到的時鐘頻率,有時包括部分模塊的布局、塊RAM的位置等。在一般設計中,只需要注意管腳位置和需要達到的時鐘頻率,邏輯端口與FPGA管腳的對應取決于PCB板的設計。

本文導航

- 第 1 頁:龍芯處理器IP核的FPGA驗證平臺設計(1)

- 第 2 頁: FPGA的典型開發流程

- 第 3 頁:驗證平臺的檢驗