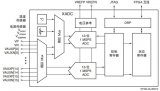

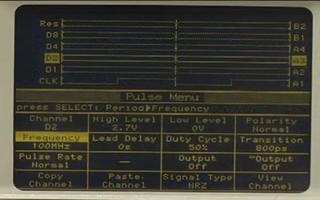

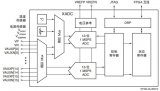

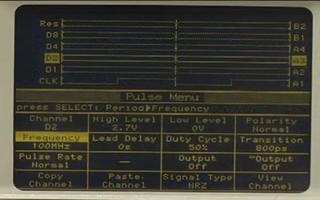

介紹一種基于FPGA技術的時間間隔測量方法,通過分析FPGA的主要技術優勢及其在工業控制領域中所處的重要地位,給出設計時間間隔測量模塊所選用的FPGA器件并進行硬件設計,以及所選

2011-10-13 14:53:47 2593

2593

FPGA的功耗高度依賴于用戶的設計,沒有哪種單一的方法能夠實現這種功耗的降低。目前許多終端市場對可編程邏輯器件設計的低功耗要求越來越苛刻。

2011-11-28 11:45:56 1117

1117 以下是筆者一些關于FPGA功耗估計和如何進行低功耗設計的知識。##關于FPGA低功耗設計,可從兩方面著手:1)算法優化;2)FPGA資源使用效率優化。

2014-12-17 09:27:28 9177

9177 本文探討了對低功耗待測器件(DUT)進行低電流測量的兩種不同方法:一是將電源、高精度數字多用表及待測器件進行串聯,二是使用高精度測量電源。應用筆記詳細介紹了怎樣配置2280S系列高進度測量直流電源

2015-01-23 16:12:46 3384

3384 整個FPGA設計的總功耗由三部分功耗組成:1. 芯片靜態功耗;2. 設計靜態功耗;3. 設計動態功耗。

2022-11-24 20:46:41 1028

1028 高云半導體基于超低功耗的非易失FPGA GW1NZ-ZV器件現已全面量產,此產品是迄今為止功耗最低的FPGA器件。 當核電壓為0.9V時,靜態功耗不到28uW。

2020-01-06 10:29:07 1823

1823 FPGA功耗的基本概念,如何降低FPGA功耗?IGLOO能夠做到如此低的功耗是因為什么?

2021-04-30 06:08:49

美高森美公司營銷總監TIM MORIN在現今日益趨向超連接的世界(hyper-connected world)中,如何保護新的設計避免被克隆、反向工程和/或篡改是一項重大挑戰。FPGA器件通過加入

2019-06-25 08:18:11

FPGA已經被廣泛用于實現大規模的數字電路和系統,隨著CMOS工藝發展到深亞微米,芯片的靜態功耗已成為關鍵挑戰之一。文章首先對FPGA的結構和靜態功耗在FPGA中的分布進行了介紹。接下來提出了晶體管

2020-04-28 08:00:00

FPGA的功耗高度依賴于用戶的設計,沒有哪種單一的方法能夠實現這種功耗的降低,如同其它多數事物一樣,降低功耗的設計就是一種協調和平衡藝術,在進行低功耗器件的設計時,人們必須仔細權衡性能、易用性、成本

2015-02-09 14:58:01

FPGA的功耗高度依賴于用戶的設計,沒有哪種單一的方法能夠實現這種功耗的降低,如同其它多數事物一樣,降低功耗的設計就是一種協調和平衡藝術,在進行低功耗器件的設計時,人們必須仔細權衡性能、易用性、成本、密度以及功率等諸多指標。

2019-11-05 07:54:43

器件有一個整體的了解。(特權同學,版權所有)Cyclone IIIFPGA系列前所未有的同時實現了低功耗、高性能和低成本,大大提高了產品競爭力。其特性以及Cyclone III FPGA體系結構為用戶

2015-04-17 12:05:21

大容量、高速率和低功耗已成為FPGA的發展重點。嵌入式邏輯分析工具無法滿足通用性要求,外部測試工具可以把FPGA內部信號與實際電路聯合起來觀察系統真實運行情況。隨著FPGA技術的發展,大容量、高速

2019-08-07 07:50:15

FPGA的功耗高度依賴于用戶的設計,沒有哪種單一的方法能夠實現這種功耗的降低,在進行低功耗器件的設計時,人們必須仔細權衡性能、易用性、成本、密度以及功率等諸多指標。

2019-08-29 07:52:29

突破FPGA系統功耗瓶頸 FPGA作為越來越多應用的“核心”,其功耗表現也“牽一發而動全身”。隨著工藝技術的越來越前沿化,FPGA器件擁有更多的邏輯、存儲器和特殊功能,如存儲器接口、DSP模塊

2018-10-23 16:33:09

的FPGACyclone III LS器件具有200K邏輯單元、8 Mbits嵌入式存儲器以及396個嵌入式乘法器,是高性能處理、低功耗應用的理想選擇,包括:●汽車●消費類●顯示●工業●視頻和圖像處理●無線具有

2019-04-15 02:21:50

目前許多終端市場對可編程邏輯器件設計的低功耗要求越來越苛刻。工程師們在設計如路由器、交換機、基站及存儲服務器等通信產品時,需要密度更大、性能更好的FPGA,但滿足功耗要求已成為非常緊迫的任務。而在

2019-07-15 08:16:56

針對I/O需求數目更多的低功耗應用,Actel可以提供IGLOO PLUS系列,規模分別是3萬、6萬和12.5萬門。和相同封裝的IGLOO器件相比,可以提供最多多出64%的I/O。其所有的器件都支持

2019-07-05 07:19:19

隨著65nm工藝的應用以及更多低功耗技術的采用,FPGA擁有了更低的成本、更高的性能以及突破性的低耗電量,具備進入更廣泛市場的條件。FPGA從業者表示,今年FPGA快速增長,而預計明年仍將是一個增長年。

2019-10-31 06:49:34

測量真實的43.2 Gb/s眼圖

2019-06-28 09:14:06

我正在嘗試測量spartan3(Spartan 3E入門套件)的靜態功耗。為此,我使用分流電阻和使能信號確保FPGA不執行應用程序。在FPGA配置之后,在我啟用應用程序運行之前,我觀察到當前的消耗

2019-05-20 13:40:40

Altera 新的 Cyclone? IV 系列 FPGA 器件鞏固了 Cyclone 系列在低成本、低功耗 FPGA市場的領導地位,并且目前提供集成收發器功能的型號。Cyclone IV 器件旨在

2017-11-13 11:22:50

嗨,我正在嘗試測量SP605評估板上Spartan6器件的功耗。第一個問題:電路板上是否有電阻,我可以通過簡單的O-scope設置來測量電壓(需要電阻以便我可以計算電流)?原理圖對于確定我能找到這個

2019-08-22 10:02:06

無論從微觀到宏觀、從延長電池壽命到減少全球變暖的溫室效應等等,各種不同因素都在迅速推動系統設計人員關注節能問題。一項有關設計優先考慮事項的最新調查指出,大部分工程師已把功耗排在首位,或者是將其緊跟在性能、密度和成本之后。在功耗方面,FPGA帶來了獨特的挑戰。為什么要設計優化FPGA功耗?

2019-08-08 07:39:45

客戶關注的問題。降低FPGA功耗是降低封裝和散熱成本、提高器件可靠性以及打開移動電子設備等新興市場之門的關鍵。

2019-09-20 06:33:32

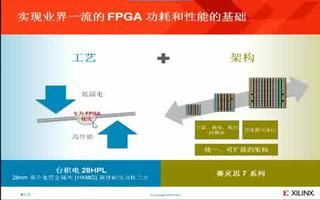

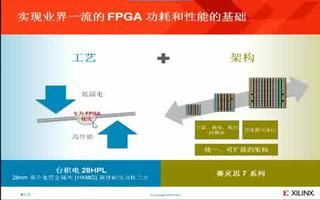

Altera公司產品和企業市場副總裁DannyBiran低功耗是一種戰略優勢 在器件的新應用上,FPGA功耗和成本結構的改進起到了非常重要的作用。Altera針對低功耗,同時對體系結構和生產工藝進行

2019-07-16 08:28:35

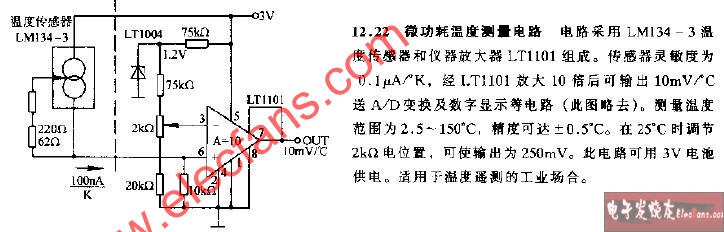

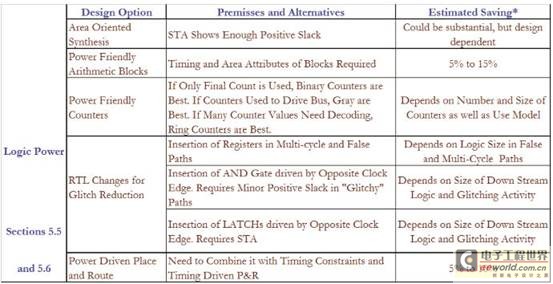

新一代 FPGA的速度變得越來越快,密度變得越來越高,邏輯資源也越來越多。那么如何才能確保功耗不隨這些一起增加呢?很多設計抉擇可以影響系統的功耗,這些抉擇包括從顯見的器件選擇到細小

2012-01-11 11:59:44

`低功耗的賽靈思 FPGA 系列使總線供電的 USB 器件設計垂手可得憑借在市場中數十億的端口數量,通用串行總線 (USB) 成為實現主機與外設之間千兆位以下連接的首選接口。不過,由于 USB 規范

2016-07-27 17:14:50

結合采用低功耗元件和低功耗設計技術在目前比以往任何時候都更有價值。隨著元件集成更多功能,并越來越小型化,對低功耗的要求持續增長。當把可編程邏輯器件用于低功耗應用時,限制設計的低功耗非常重要。本文將討論減小動態和靜態功耗的各種方法,并且給出一些例子說明如何使功耗最小化。

2019-07-12 06:38:08

FPGA 實驗板實物圖如圖所示這是整板的外設器件的示意圖。FPGA 實驗板接口芯片連接如圖所示二、電源電路與任何電子元器件一樣,FPGA 器件需要有電源電壓的供應才能工作。尤其對于規模較大的器件,其功耗也相對較高,其供電系統的好壞將直接影響到整個開發系統的穩定性。所以,設計出高效率、高性能的 FP

2021-11-17 07:46:27

的方式開關器件,對比整機電流的變化值,估算這些器件的工作電流。硬件拆解法電路板在設計之初,為了方便功耗的驗證與測量,可以設置一些0R(零歐姆)電阻,串接在各個電源回路里。拆解方法:如電源回路中串接了一個

2022-10-14 11:18:18

大家好,我想測量我的Virtex 5 FPGA在ML505板上的功耗(該板實際上是XUPV5-LX110T),通過在這個論壇中搜索,似乎唯一的方法是測量板上特定電阻的電流(電壓) 。我在這個論壇上

2020-06-13 19:33:07

設計出色的低功耗應用需要考慮哪些因為? 如何為低功耗應用選擇正確的uC外圍器件?

2021-04-08 06:53:11

減小動態和靜態功耗的方法有哪些?如何使FPGA設計中的功耗最小化?

2021-05-08 07:54:07

復雜器件專業技術相結合,將為系統供應商提供低功耗的芯片方案,供他們在此基礎上持續提高帶寬容量,并完成更智能的處理。此外,TPACK提供的芯片解決方案可以導入到最新的FPGA中,進一步降低功耗。最終實現

2019-07-31 07:13:26

如何才能實現降低FPGA設計的功耗?

2021-04-29 06:47:38

FPGA的功耗高度依賴于用戶的設計,沒有哪種單一的方法能夠實現這種功耗的降低,如同其它多數事物一樣,降低功耗的設計就是一種協調和平衡藝術,在進行低功耗器件的設計時,人們必須仔細權衡性能、易用性、成本、密度以及功率等諸多指標。

2019-08-15 08:28:42

Actel公司的ILGOO系列器件是低功耗FPGA產品,是在便攜式產品設計中替代ASIC和CPLD的最佳方案。它在Flash*Freeze模式時的靜態功耗最低可達到2μW,電池壽命是采用主流PLD

2020-05-13 08:00:00

。但并不是所有工藝技術都一樣。例如,對于 90 nm 技術來說,Virtex-4 器件與其他 90 nm FPGA 技術之間在靜止功耗方面存在顯著差異,然而,在靜止功耗隨工藝技術縮小而增加的同時,動態

2020-12-30 08:00:00

怎么用MCU測量當前系統的運行功耗

2023-10-13 07:20:43

Actel公司的ILGOO系列器件是低功耗FPGA產品,是在便攜式產品設計中替代ASIC和CPLD的最佳方案。它在Flash*Freeze模式時的靜態功耗最低可達到2μW,電池壽命是采用主流PLD

2019-07-31 07:05:45

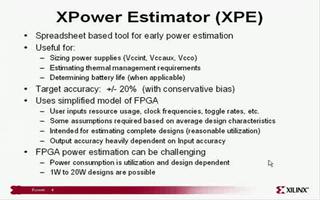

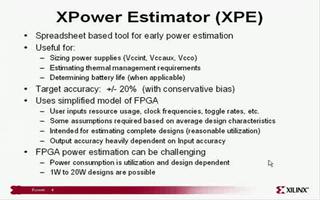

` 在項目設計初期,基于硬件電源模塊的設計考慮,對FPGA設計中的功耗估計是必不可少的。筆者經歷過一個項目,整個系統的功耗達到了100w,而單片FPGA的功耗估計得到為20w左右,有點過高了,功耗

2014-08-21 15:31:23

測量 ADC 的真實錯誤率讓客戶能夠基于不同條件在自己的工作臺上測量位錯誤率提供適用于 TI 低成本 FPGA 平臺的固件,還有簡單的 GUI 用于監控長時間的錯誤率

2022-09-22 06:32:27

想要學習低功耗設計,面臨的第一個問題就是如何測量休眠時的功耗

正常工作時的電流和休眠時的電流相差太多,用萬用表肯定不合適。

請問使用什么設備來測量?

2023-11-02 06:40:26

設計技巧為什么能夠節省功耗?降低FPGA功耗的設計技巧有哪些?

2021-04-30 06:04:19

介紹一種基于FPGA技術的時間間隔測量方法,通過分析FPGA的主要技術優勢及其在工業控制領域中所處的重要地位,給出設計時間間隔測量模塊所選用的FPGA器件并進行硬件設計,以及

2010-12-31 17:29:36 25

25

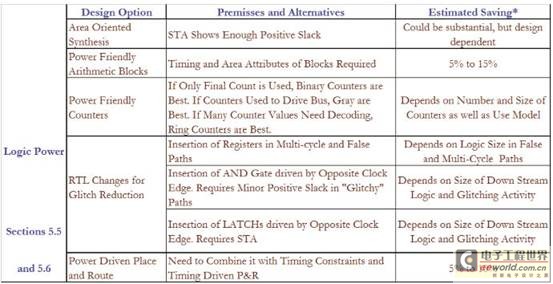

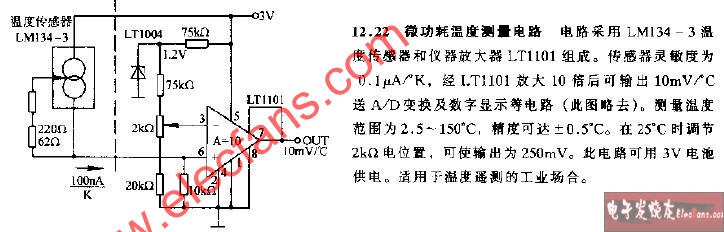

微功耗溫度測量電路

2009-02-19 22:20:23 1774

1774

具有低功耗意識的FPGA設計方法

ILGOO系列低功耗FPGA產品

Actel公司的ILGOO系列器件是低功耗FPGA產品,是在便攜式產品設計中替代ASIC和CPLD的最

2009-11-26 09:41:19 676

676

便攜式產品具有低功耗意識的FPGA設計方法

ILGOO系列低功耗FPGA產品

Actel公司的ILGOO系列器件是低功耗FPGA產品,是在便攜式產品設計中替

2009-11-30 09:46:56 674

674

低功耗Cyclone IV FPGA

Altera公司宣布,開始批量發售Cyclone IV FPGA。公司還宣布開始提供基于Cyclone IV GX的收發器入門開發套件。Altera的Cyclone IV FPGA設計用于無線、固網、廣播

2010-03-31 10:42:42 1431

1431 FPGA的功耗高度依賴于用戶的設計,沒有哪種單一的方法能夠實現這種功耗的降低,在進行低功耗器件的設計時,人們必須仔細權衡性能、易用性、成本、密度以及功率等諸多指標

2010-07-01 11:08:43 465

465 FPGA的功耗高度依賴于用戶的設計,沒有哪種單一的方法能夠實現這種功耗的降低,如同其它多數事物一樣,降低功耗的設計就是一種協調和平衡藝術,在進行低功耗器件的設計時

2010-07-06 11:06:10 981

981 本文將介紹FPGA的功耗、流行的低功耗功能件以及影響功耗的用戶選擇方案,并探討近期的低功耗研究,以洞察高功率效率FPGA的未來趨勢。

功耗的組成部分

2010-08-27 10:57:21 1637

1637

自從Xilinx推出FPGA二十多年來,研發工作大大提高了FPGA的速度和面積效率,縮小了FPGA與ASIC之間的差距,使FPGA成為實現數字電路的優選平臺。今天,功耗日益成為FPGA供應商及其客戶關注的問題。降低FPGA功耗是縮減封裝和散熱成本、提高器件可靠性以及打開移

2011-03-15 14:58:34 31

31 萊迪思半導體公司(NASDAQ: LSCC)近日宣布,即可獲取增加至非常成功的LatticeECP3?FPGA系列的低功耗、高速和迷你封裝器件。

2012-02-04 09:59:34 783

783 Cyclone V FPGA功耗優勢:采用低功耗28nm FPGA活的最低系統功耗(英文資料)

2012-09-05 16:04:11 40

40 白皮書 :采用低成本FPGA實現高效的低功耗PCIe接口 了解一個基于DDR3存儲器控制器的真實PCI Express (PCIe) Gen1x4參考設計演示高效的Cyclone V FPGA怎樣降低系統總成本,同時實現性能和功耗

2013-02-26 10:04:25 72

72 一種可測量真實放電量的局部放電實驗電路

2017-01-22 13:20:25 23

23 測量元器件

2017-03-04 17:53:55 5

5 基于FPGA的低頻相位測量系統設計_李寶營

2017-03-19 11:38:26 2

2 CycloneIVFPGA器件系列概述

2017-03-17 14:41:35 7

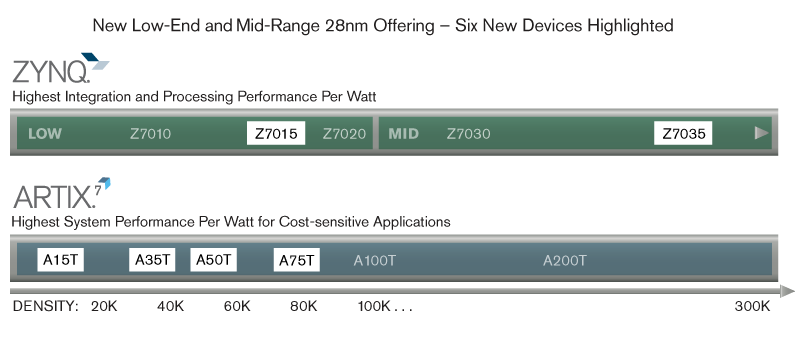

7 賽靈思 Spartan?-7 系列提供了一系列高效、低成本的 FPGA 器件。這些器件經過專門設計,能滿足低成本市場的特殊需求。 摘要 Spartan?-7 FPGA 將高性能 28nm 可編程

2017-11-16 15:15:54 8367

8367

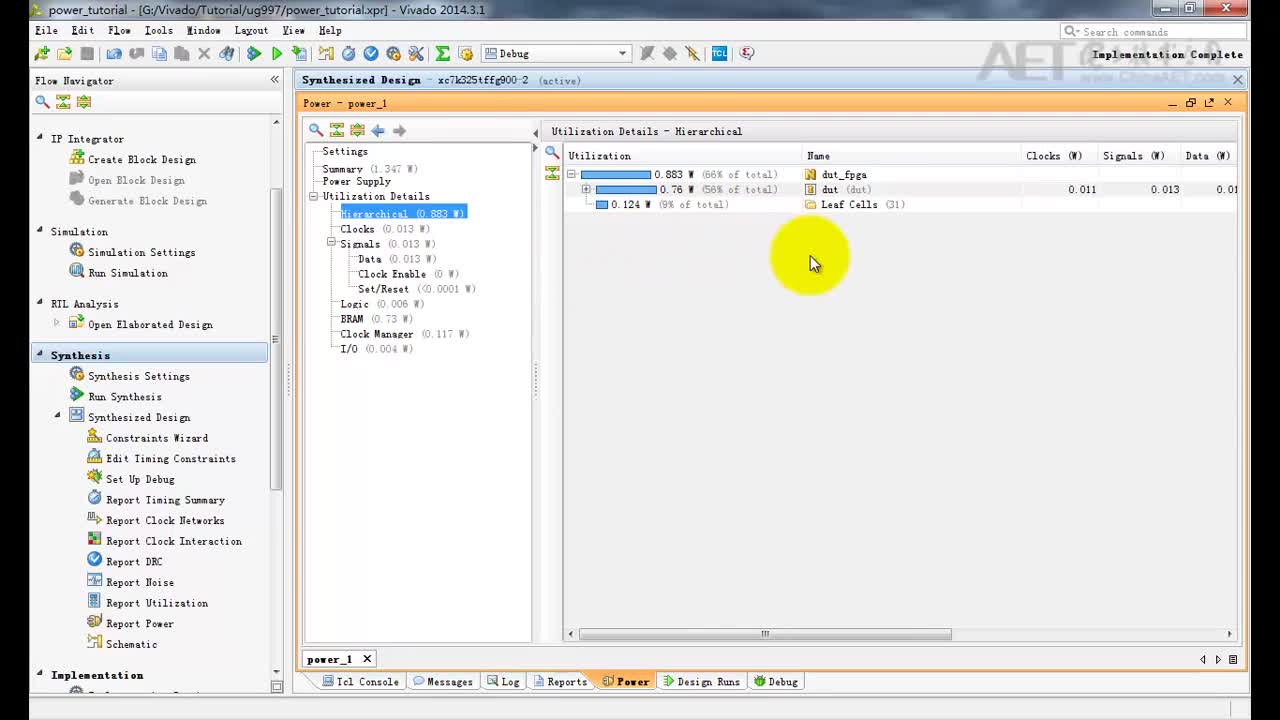

資源、速度和功耗是FPGA設計中的三大關鍵因素。隨著工藝水平的發展和系統性能的提升,低功耗成為一些產品的目標之一。功耗也隨之受到越來越多的系統工程師和FPGA工程師的關注。Xilinx新一代開發工具Vivado針對功耗方面有一套完備的方法和策略,本文將介紹如何利用Vivado進行功耗分析和優化。

2017-11-18 03:11:50 4873

4873 為設計尋找“完美”FPGA 的重要性日漸升級,其中功耗已成為主要考慮因素。功耗管理在大部分應用中都非常關鍵。某些標準已為單卡或者單個系統設定了功耗上限。鑒于此,設計人員必須在設計過程中更早地對功耗

2017-11-22 15:03:01 2573

2573 設計者通過優化自己的設計和注意某些具體情況,可以在FPGA設計中實現低功耗。通過一款具體的FPGA產品了解其低功耗的解決方式,為設計提供了指導。FPGA均可在相應的操作環境下進行仿真,從而了解功耗

2017-11-23 10:37:23 1248

1248 ? FPGA器件,它們在器件、設計和系統層次上的安全特性都比其他領先FPGA制造商更先進。新的數據安全特性現已成為美高森美主流SmartFusion2 SoC FPGA和 IGLOO2 FPGA器件

2018-04-28 15:50:00 880

880 采用賽靈思7系列FPGA滿足嚴格的功耗預算

2018-06-05 13:45:00 3257

3257

本演示中,我們將介紹利用 XPower 估計器(XPE)工具精確估計 Virtex?-5 器件的功耗所需的步驟。我們還通過在 ML550 開發板 - 進行詳細的功耗測量的首選平臺 - 上進行測量演示了 Virtex?-5 器件的低功耗特性。

2018-06-06 02:45:00 2951

2951

看看LatticeECP3 FPGA的功耗是多么的低,無論是在實驗室中測量,還是利用萊迪思的功耗計算器軟件計算。 LatticeECP3是業界最低功耗的配備SERDES的FPGA。

2018-06-15 13:36:00 4990

4990

項目設計初期會選型,工程師根據資源、IO、硬核、IP等選擇對應型號的FPGA。功耗部分xilinx提供了XPE表格(Xilinx PowerEstimator),這個XPE支持zynq、目前也有各個系列的器件列表,包括最新的ultrascale + 。

2018-06-27 09:05:00 5224

5224

關鍵詞:FPGA , 低功耗 , RTL 在項目設計初期,基于硬件電源模塊的設計考慮,對FPGA設計中的功耗估計是必不可少的。筆者經歷過一個項目,整個系統的功耗達到了100w,而單片FPGA的功耗

2018-09-07 14:58:01 381

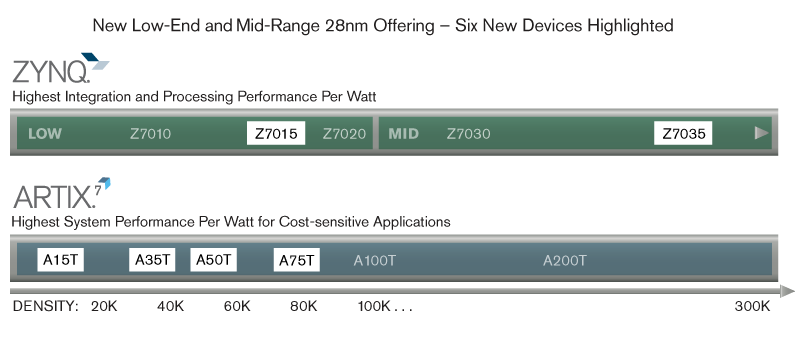

381 持續創新 28HPL 高性能低功耗工藝,成就跨越全新中低端器件,和 Artix-7 FPGA、Kintex-7 FPGA 及 Zynq-7000 SoC 產品系列的全新低功耗工業速度等級的器件敬請

2019-08-01 09:07:32 3066

3066

基站功耗與工作溫度也密切相關。通常,工作溫度越高,器件的漏電流越大,基站功耗也就越大。

2019-11-08 11:47:04 705

705 在針對大批量應用開發系統時,要考慮的一個重要因素是成本。有多個方面會影響總體擁有成本,而不僅僅是每個元器件的價格。這包括硅片的功耗要求、材料(BOM)總成本、設計和測試系統的工程師的效能等。選擇FPGA供應商很重要,要考慮影響系統成本的方方面面,這體現在整個產品設計周期中。

2020-07-17 18:08:34 1718

1718 的功耗高度依賴于用戶的設計,沒有哪種單一的方法能夠實現這種功耗的降低。目前許多終端市場對可編程邏輯器件設計的低功耗要求越來越苛刻。在消費電子領域,OEM希望采用FPGA的設計能夠實現與ASIC相匹敵的低功耗。 盡管基于90nm工藝的FPGA的功耗已低

2020-10-28 15:02:13 2498

2498 的功耗高度依賴于用戶的設計,沒有哪種單一的方法能夠實現這種功耗的降低。目前許多終端市場對可編程邏輯器件設計的低功耗要求越來越苛刻。在消費電子領域,OEM希望采用FPGA的設計能夠實現與ASIC相匹敵的低功耗。 盡管基于90nm工藝的FPGA的功耗已低

2020-10-26 18:51:16 2583

2583 并不是所有元件都具有相同的靜止功耗。根據普遍規則,器件工藝技術尺寸越小,泄漏功耗越大。但并不是所有工藝技術都一樣。例如,對于 90 nm 技術來說,Virtex-4 器件與其他 90 nm FPGA 技術之間在靜止功耗方面存在顯著差異,

2021-01-08 17:46:48 5063

5063 功耗是我們關注的設計焦點之一,優秀的器件設計往往具備低功耗特點。在前兩篇文章中,小編對基于Freez技術的低功耗設計以及FPGA低功耗設計有所介紹。為增進大家對低功耗的了解,以及方便大家更好的實現低功耗設計,本文將對FPGA具備的功耗加以詳細闡述。如果你對低功耗具有興趣,不妨繼續往下閱讀哦。

2021-02-14 17:50:00 6069

6069 與現有的中端FPGA相比,得益于專為低功耗設計的可編程結構、功耗優化的嵌入式存儲器和DSP、低功耗高性能SERDES與I/O設計、內置協議邏輯等全方位優化措施,Avant系列產品的功耗比同類競品器件低2.5倍。

2023-01-04 11:32:11 342

342 選擇FPGA器件廠商、器件系列、工具集等,很大程度上還是要考慮設計團隊成員的設計經歷和偏好。話說“就熟不就生”,因為這在很大程度上會決定了設計復雜性高低和項目進度周期的快慢。當然了,其它因素諸如成本、資源、功耗、可移植、可升級等等也是需要考量的。總而言之,這也是一個需要綜合考慮的權衡決策。

2023-02-13 11:26:18 514

514 點擊上方 藍字 關注我們 ? FPGA 高級設計之實現功耗優化 與ASICs(Application Specific Integrated Circuits)比較,相似的邏輯功能,用FPGA來實現

2023-05-19 13:50:02 815

815 摘要:萊迪思(Lattice )半導體公司在這應用領域已經推出兩款低成本帶有SERDES的 FPGA器件系列基礎上,日前又推出采用富士通公司先進的低功耗工藝,目前業界首款最低功耗與價格并擁有SERDES 功能的FPGA器件――中檔的、采用65nm工藝技術的 LatticeECP3系列。

2023-10-27 16:54:24 237

237 雙脈沖測試的基本原理是什么?雙脈沖測試可以獲得器件哪些真實參數? 雙脈沖測試是一種常用的測試方法,用于測量和評估各種器件的性能和特性。它基于一種簡單而有效的原理,通過發送兩個脈沖信號并分析其響應

2024-02-18 09:29:23 234

234

電子發燒友App

電子發燒友App

評論