電源管理一直是FPGA設計中的關鍵問題。現有一種新方法可用于測量真實FPGA器件的功耗估計值

現代的FPGA 芯片能夠開發高性能應用,但在這些設計中電源管理通常是一大限制因素。FPGA 器件的資源使用最能決定設計的容量和處理速度,但是增加資源就會提高功耗。更高的功耗會提高運行成本、面積要求和結溫,而設計人員必須用更多的氣流和冷卻系統來解決結溫問題。

由于開發板或系統的總功耗極其重要,因此設計人員必須設置一個功耗預算,在資源使用和功耗問題方面兼顧平衡。所以,事先預測系統潛在功耗的能力可幫助設計人員獲得先發優勢。

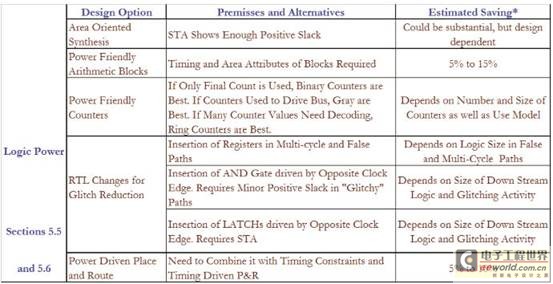

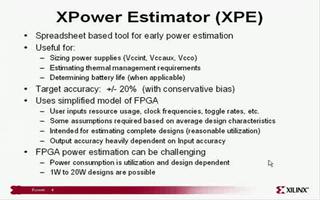

對于實現前的功耗評估,賽靈思可提供一些工具根據用戶輸入內容或綜合報告進行功耗估計。其中一款工具就是賽靈思功耗估計器(Power Estimator,XPE)電子數據表。這款基于Excel 的功耗估計工具能讓您輸入資源使用、翻轉率和時鐘頻率等設計屬性,并根據器件信息計算估計的功耗值。另一款常用的工具是賽靈思功耗分析器(Power Analyzer,XPA)。在布局和布線后,XPA 會導入已生成的NCD 文件,并利用實現詳細信息和仿真結果(而非用戶輸入)來更加準確地估計功耗。

作為備選方案,我們設計出一種新方法來測量真實器件上FPGA 設計的功耗估計值。為模擬不同的實現方案,我們創建了一個獨立于器件的通用VHDL 設計,其有可能實現在FPGA 運行時通過串行通道改變激活的資源(即DSP slice、Block RAM 和slice 寄存器)的數量及相應的運行條件(結溫、時鐘頻率和翻轉率)。 我們的這種技術可以同時監控電源的電流和電壓大小,便于我們輕松觀察器件在不同資源使用和環境條件下的動態功耗特性。

我們已在賽靈思KC702 評估板上實現了該設計。不過,只要您的FPGA 器件支持設計中所使用的IP核,您只需做輕微修改也可在任何其它器件上實現該設計。

另一種使用該技術的方法可能是作為面向FPGA 板的VHDL 測試設計。我們假設最近設計了一個通用型Kintex?-7 開發板。客戶可在不斷變化的環境條件下利用未知的資源容量在開發板上實現任何設計。為了確保開發板的穩定性和穩健性,我們需要在最高和最低所需的環境溫度下強加器件的工作極限,并驗證FPGA 能夠支持不同的資源使用情況。然而,測試每種資源使用方案需要從頭開始開發一款全新的VHDL 設計,這會耗費太多時間。我們推薦的方法可幫助設計人員靈活地根據需要對測試設計進行實時控制。

?

實現細節

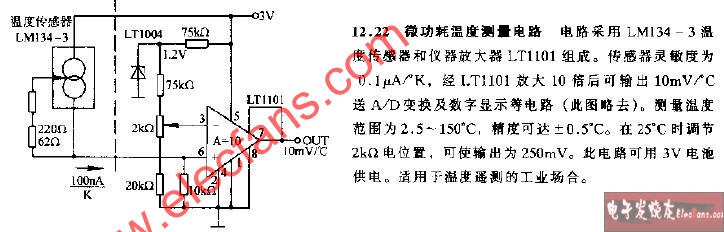

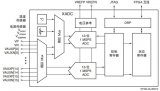

我們設法讓實現方案盡可能的簡單,以避免生成作為邏輯使用的s l i c e LUT,因為我們無法對其功耗進行控制。實現slice 寄存器最簡單的方法是將它們組合為移位寄存器模塊。圖1a中的方框圖給出了slice 寄存器的實現方法。 這里需要注意一個簡單的問題,當我們嘗試創建slice 寄存器時,綜合工具常常將slice LUT 作為32 位移位寄存器(SRL32)使用,而不是使用slice 寄存器。您也可以利用以下VHDL 屬性來強制綜合軟件使用slice寄存器:

LogiCORETM 模塊存儲器生成器創建作為單端口RAM 的Block RAM。將一個數位持續翻轉的16 位字不停寫入激活BRAM 的隨機地址中,從而使它們保持被占用狀態。圖1b 是單個BRAM 組件的方框圖。同樣,我們使用DSP slice 將一個25位被乘數與一個18 位乘數相乘,得到一個43 位輸出, 這就是單個DSP48E1 可以處理的最大字寬。所有DSP 組件的被乘數會被定期修改,從而使DSP 消耗動態功耗,如圖1c 所示。然而,綜合工具試圖在綜合過程中刪除資源,因為這些模塊的輸出未與任何輸出引腳連接。您可以使用以下屬性使資源保持不變:

在該方案中,您可通過控制時鐘使能信號來激活資源。時鐘禁用后的資源只消耗非常小的功耗,可在設計中忽略不計。具體來說,具有100%翻轉率的50 個DSP slice 的功耗為0.112 瓦,而當它們的時鐘使能信號取消斷言時功耗為0.001 瓦。不同使用率下的結果幾乎相同。因此,每個資源組件都由時鐘使能信號通過串行通信進行控制的設計無需采用新的設計和實現步驟即可立即仿真出改變使用率時的情況。

資源的平均翻轉率是顯著影響功耗的重要因素。翻轉率是指特定資源在每個時鐘周期內輸出信號的跳變次數。您可以交替改變資源的輸入以使輸出在每個周期都改變其狀態,從而實現恒定的100% 翻轉率。例如,要調整DSP slice 的翻轉率,您可以選擇兩個被乘數(連續交替)和一個乘數,這樣輸出的每位在每個周期中都會發生變化。輸入信號的交替速率決定資源的翻轉率;因此,我們通過串行通道就能即時控制某個資源類型的翻轉率。

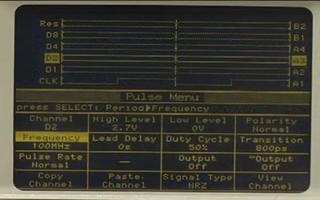

此外,功耗還與時鐘頻率直接成正比。我們使用混合模式時鐘管理器(MMCM)生成具有可變頻率的時鐘。MMCM 輸出的頻率、相位和占空比由一組寄存器決定,而且一般只當實現設計和生成bit 流文件時才進行初始化。然而,MMCM 的動態重配置端口使我們能在FPGA 運行時改變輸出時鐘等特性。時鐘的相位和占空比不在考慮范圍內,因為相位并不影響功耗,而占空比在大多數情況下也并不會改變。

另一方面,頻率與功耗高度相關。MMCM 的內部工作機理是,VCO 頻率由CLKOUT0_DIVIDE 寄存器的值進行分頻,以獲得所需的輸出頻率。我們根據賽靈思應用指南XAPP888 中介紹的狀態機算法為寄存器賦予新值,實現無毛刺轉換。與此同時,我們根據圖形用戶界面(GUI)中的用戶輸入實時改變設計的時鐘頻率。然后,我們能方便地觀察不同頻率下設計的功耗特性。

高溫條件下的功耗行為是另一項需要認真觀察和驗證的重要問題。芯片的內核溫度取決于開發板設計、處理速度、環境溫度、散熱片和風扇的氣流。在我們的設計中,我們利用簡單的PWM 開關控制器改變位于FPGA 芯片頂部的風扇的速度,從而局部地控制結溫。此外,您也可以使用熱風槍等外部加熱工具來縮短加熱時間。

用片上傳感器測量內核溫度,并通過LogiCORE XADC 向導生成模數轉換器XADC。當您在GUI 中輸入參考溫度值時,GUI 通過串行通道將參考值發送到器件,并與片上傳感器測量到的內核溫度進行比較。通過控制風扇的速度將結溫穩定在所需的水平上。這樣,您就可以觀察功耗情況并繪制與內核溫度的走勢圖,從而驗證是否滿足設計的功耗預算,以及功耗在所需的加熱特性下是否保持在關鍵限值以內。

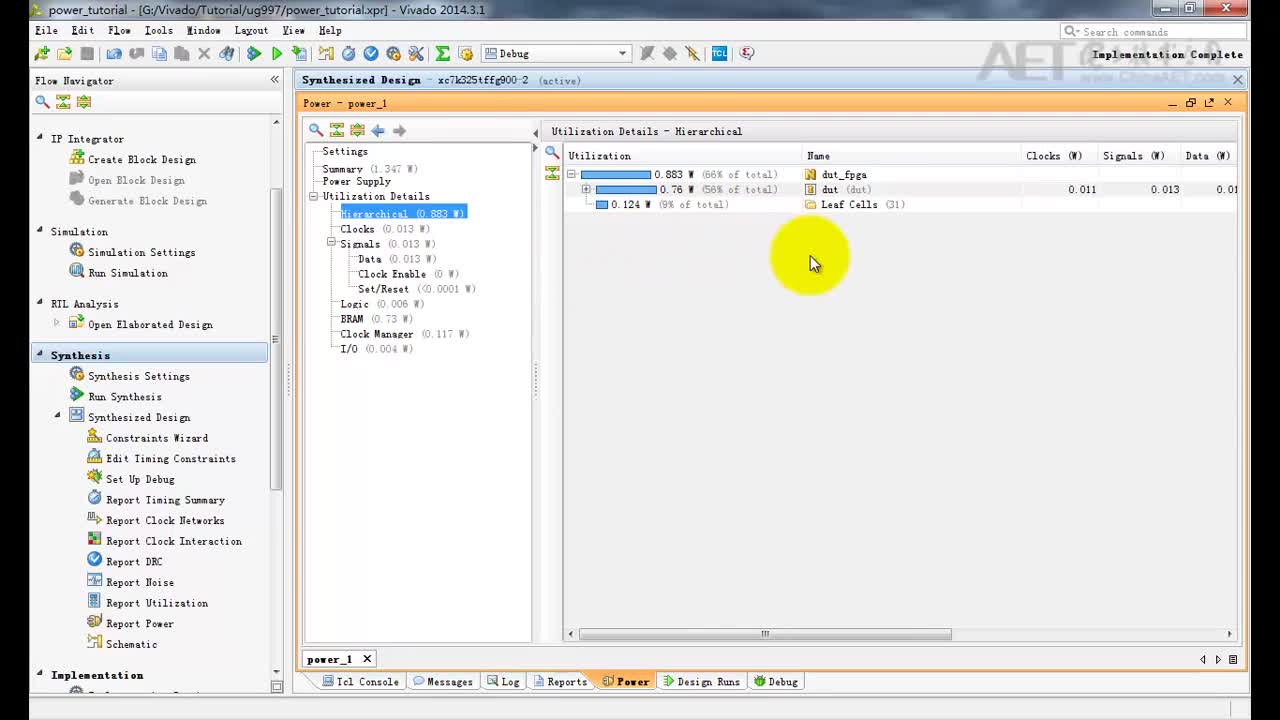

圖形用戶界面可用來與FPGA 器件通信,以改變上述參數。圖2 給出了GUI 的屏幕截圖。我們首先通過標準UART 利用其中一個可用端口連接到器件。然后,我們打開賽靈思功耗估計器將估計值與測量值進行比較。GUI 立即為使用默認參數值的估計功耗和實際功耗繪制功耗與時間關系圖。您可在相關面板中修改這些參數,并在資源(Resource)面板中利用翻轉率指定所用的slice 資源數量。使用掃描(Utilization Sweep)面板在等間隔下從0% 至100% 掃描特定資源的使用率,并利用每個間隔的測量功耗值繪制功耗與使用率關系圖。

?

同樣,您可在時鐘選擇(Clock Select)面板中改變MMCM 的輸出并掃描時鐘頻率。在下一欄的Vccint 面板中可測量和連續繪制出FPGA 芯片的電源電壓。同時,內核溫度(Core Temperature)面板顯示并繪制出內核溫度。用戶可在提供的對話框中輸入參考溫度以改變結溫。

您可利用集成在KC702 開發板上的德州儀器(Texas Instruments)UCD9248 數字PWM 系統控制器測量電源的電壓和電流電平。這種用于電源轉換器的多軌和多相位PWM 控制器支持電源管理總線(PMBus)通信協議。其PWM 信號可驅動用于調節Vccint 電源電壓的UCD7242 集成電路。一組PMBus 命令可用于配置IC功能。UCD7242 包含片上電壓與電流感應電路,并與UCD9248 進行通信。我們的GUI 軟件不斷向該器件發送相應的PMBus 命令,同時接收標準PMBus 數據格式的DC/DC 轉換器的電壓和電流值。然后,我們將收到的字節轉換為實際數值,并獲得電源的電壓和電流電平。

在高溫下運行復雜、擁塞的設計可能會擾亂電源電壓電平。不幸的是,FPGA 芯片對于輸入電壓的容差范圍較小。超過該電平范圍會導致芯片上的功能失效或者永久損壞。因此,您在設計完開發板后,還需要測試嚴苛工作條件下電壓電平的穩定性。Vccint 面板可用來觀察和驗證設計開發板的電源系統是否能夠承受高溫下進行高速處理時的電壓變化。

設計人員需要始終謹記的重要一點是:由于制造工藝變化,每個器件都會有不同的功耗。例如,在Virtex-7 FPGA 芯片制造完成后,會在測試階段確定足夠讓芯片正確運行的最小電壓源電平并寫入電熔絲。將穩壓器輸出調節至這個最小電壓電平可以改變靜態功耗。因此,靜態功耗的偏移會導致XPE 與我們的設計在結果上出現差異。例如,XPE 中估計的Kintex-7 芯片的靜態功耗在典型情況與最差情況時計算相差0.7 瓦。

完美匹配XPE

我們在很多具有可變因素的不同設計方案中對我們的設計進行了測試,以確保其精確性和可靠性。同時,還在測量值的示意圖中繪出XPE 的估計結果,從而將功耗估計值與實際測量值進行比較。

通過最初將資源使用率從零至設計最大值掃描的設計實現可觀察Kintex-7 器件的功耗行為。圖3 給出了掃描一種資源類型的使用率過程中功耗的變化情況。直線和虛線分別代表實際功耗測量值和XPE 的估計值。我們可以看到即使在使用率和功耗處于高值時兩條曲線依然靠得非常緊密。

?

這些結果表明賽靈思功耗估計器計算值與實際測量值一致,可以準確地預測功耗。此外,我們還可以斷定我們推薦的方法能夠起到預期效果,并且可以作為XPE 的替代方案。更好的選擇是將兩種方法結合使用。同時采用XPE 和我們的方法來測試設計可對結果進行雙重檢查,確保您在XPE中修改數字時不會犯任何錯誤。例如,如果您沒有在XPE 中正確輸入時鐘的平均扇出數字,或者誤解了一個概念并錯誤填寫對話框,那么得到的示意圖就無法重合,即表明有錯誤存在,這樣您就可以校正輸入值,防止出現誤導性的估算結果。

FPGA 開發板的額定規范,例如最大功耗或允許的內核溫度范圍,總是包含在開發板的數據手冊中。不過,具有較高資源使用率和時鐘頻率的設計會超出這些額定值。因此,必須確認功率調節器能為器件提供足夠的電流,而且散熱系統足以將溫度保持在FPGA 設計的臨界值以內。我們的方法可通過增加資源使用和時鐘頻率來測試開發板的可靠性能否滿足高性能要求。這種測試有助于確定開發板上實現的設計所具備的最高信號處理速率。此外,我們還可以了解是否需要升級開發板的功能和系統的冷卻機制。

測試結果表明了我們的方法能夠可靠地控制資源使用和評估功耗,因此工程師在設計前期階段就多了一種電源管理選項。在采取進一步功能改進后,例如增加JTAG 接口、完全獨立于器件的VHDL 代碼以及通用的電流感應系統,這項設計將會成為FPGA 項目的關鍵工具。

電子發燒友App

電子發燒友App

評論