淺析FPGA的應(yīng)用領(lǐng)域

FPGA 最初的應(yīng)用領(lǐng)域也是傳統(tǒng)的應(yīng)用領(lǐng)域,通信領(lǐng)域,但隨著信息產(chǎn)業(yè)以及微電子計(jì)數(shù)發(fā)展,F(xiàn)PGA的應(yīng)....

掌握Verilog FPGA設(shè)計(jì)和驗(yàn)證方法是AI時(shí)代系統(tǒng)設(shè)計(jì)師的生命線

? ?在人工智能時(shí)代,AI的算法不斷推陳出新,對(duì)于硬件的算力和靈活度要求很高。FPGA的靈活性剛好符....

FPGA到底是什么?,F(xiàn)PGA工程師核心競(jìng)爭(zhēng)力是什么?

Intel和AMD都斥巨資收購了領(lǐng)先的 FPGA 公司。撇開相對(duì)較小的嵌入式計(jì)算和通信/互聯(lián)網(wǎng)市場(chǎng),....

PCI總線地址空間與系統(tǒng)地址空間的關(guān)系

1、PCI地址空間 PCI總線具有32位數(shù)據(jù)/地址復(fù)用總線,所以其存儲(chǔ)地址空間為2的32次方=4GB....

verilog的時(shí)鐘分頻與時(shí)鐘使能

時(shí)鐘使能電路是同步設(shè)計(jì)的基本電路,在很多設(shè)計(jì)中,雖然內(nèi)部不同模塊的處理速度不同,但由于這些時(shí)鐘是同源....

校招FPGA筆試講解

1.對(duì)于同步fifo,每100個(gè)cycle可以寫入80個(gè)數(shù)據(jù),每10個(gè)cycle可以讀出8個(gè)數(shù)據(jù),f....

FPGA學(xué)習(xí)-IO延遲的約束方法

為了對(duì)設(shè)計(jì)外部的時(shí)序情況進(jìn)行精確建模,設(shè)計(jì)者必須設(shè)定輸入和輸出端口的時(shí)序信息。Vivado只能識(shí)別出....

FIR濾波器和IIR濾波器的區(qū)別與聯(lián)系

1.根據(jù)沖激響應(yīng)的不同,將數(shù)字濾波器分為有限沖激響應(yīng)(FIR)濾波器和無限沖激響應(yīng)(IIR)濾波器。....

Vivado使用技巧-支持的Verilog語法

復(fù)雜的電路設(shè)計(jì)通常使用自頂向下的設(shè)計(jì)方法,設(shè)計(jì)過程中的不同階段需要不同的設(shè)計(jì)規(guī)格。比如架構(gòu)設(shè)計(jì)階段,....

Vivado使用技巧-HDL編寫

在 Vivado 中進(jìn)行HDL代碼設(shè)計(jì),不僅需要描述數(shù)字邏輯電路中的常用功能,還要考慮如何發(fā)揮Xil....

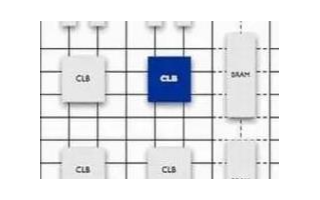

Xilinx FPGA中的基礎(chǔ)邏輯單元

Xilinx FPGA的組成部分 本文是以Xilinx Kintex UltraScale+ 系列為....

FPGA上電時(shí)序加載過程詳解

目前,大多數(shù) FPGA 芯片是基于 SRAM 的結(jié)構(gòu)的, 而 SRAM 單元中的數(shù)據(jù)掉電就會(huì)丟失,因....

FPGA基礎(chǔ)資源之IOB的應(yīng)用

FPGA基礎(chǔ)資源之IOB的應(yīng)用 1.應(yīng)用背景 在我們做時(shí)序約束時(shí),有時(shí)候需要對(duì)FPGA驅(qū)動(dòng)的外圍器件....

基于LVDS差分接口之IOSERDES的高速串行通信

項(xiàng)目涉及5片F(xiàn)PGA之間的多機(jī)通信,1片主FPGA,4片從FPGA,5片F(xiàn)PGA采用星形連接的拓?fù)浣Y(jié)....

基于LVDS差分接口之IOSERDES的高速串行通信

項(xiàng)目涉及5片F(xiàn)PGA之間的多機(jī)通信,1片主FPGA,4片從FPGA,5片F(xiàn)PGA采用星形連接的拓?fù)浣Y(jié)....

FPGA學(xué)習(xí)-DDR3

一、DDR3簡(jiǎn)介 ? ? ? ? DDR3全稱double-data-rate 3 synchron....

基于FPGA實(shí)現(xiàn)PN序列發(fā)生器的設(shè)計(jì)

近年來,擴(kuò)頻通信技術(shù)在移動(dòng)通信、個(gè)人通信、室內(nèi) 無線通信 以及衛(wèi)星通信中得到越來越廣泛的應(yīng)用。對(duì)于D....

鎖存器、觸發(fā)器、寄存器的關(guān)聯(lián)與區(qū)別及其相應(yīng)的verilog描述

1:鎖存器、觸發(fā)器、寄存器的關(guān)聯(lián)與區(qū)別 首先應(yīng)該明確鎖存器和觸發(fā)器是由與非門之類的東西構(gòu)成。尤其是鎖....

FPGA 結(jié)構(gòu)分析 -IO 資源

關(guān)于 FPGA 的 IO資源分析共分為三個(gè)系列進(jìn)行具體闡述,分別為: IO資源:分析FPGA IO資....

FPGA學(xué)習(xí)-Verilog例化說明

Verilog 例化說明 1.什么是模塊例化?為什么要例化? 模塊例化可以理解成模塊調(diào)用。對(duì)于一個(gè) ....

關(guān)于多周期路徑約束

一、什么是多周期路徑約束? 不管是quartus中還是在Vivado中,默認(rèn)的建立時(shí)間和保持時(shí)間的檢....

詳解浮點(diǎn)運(yùn)算的定點(diǎn)編程

我們使用的處理器一般情況下,要么直接支持硬件的 浮點(diǎn)運(yùn)算 ,比如某些帶有FPU的器件,要么就只支持定....

FPGA學(xué)習(xí)-SystemVerilog語言簡(jiǎn)介

SystemVerilog是一種硬件描述和驗(yàn)證語言(HDVL),它基于IEEE1364-2001 V....

FPGA需要跑多快?影響FPGA計(jì)算性能的幾大因素

FPGA ?vs. ASIC 專用芯片ASIC的開發(fā)流程是:設(shè)計(jì)、驗(yàn)證、流片、封裝、測(cè)試; 而FPG....

浮點(diǎn)與定點(diǎn)運(yùn)算以及數(shù)據(jù)定標(biāo)和精度問題

計(jì)算機(jī)體系結(jié)構(gòu)中浮點(diǎn)和定點(diǎn)數(shù)據(jù)的表示 1、定點(diǎn)數(shù): 定點(diǎn)數(shù)指小數(shù)點(diǎn)在數(shù)中的位置是固定不變的,通常有定....

至芯科技12年不忘初心、再度起航12月17日北京中心FPGA工程師就業(yè)班開課、線上線下多維教學(xué)、歡迎咨詢!

點(diǎn)擊上方 藍(lán)字 關(guān)注我們 背景: 行業(yè)迅速崛起,但人才缺口大 近幾年,在FPGA的需求持續(xù)走高時(shí),F(xiàn)....

FPGA基礎(chǔ)之HLS

1、HLS簡(jiǎn)介 HLS(High-Level Synthesis)高層綜合,就是將 C/C++的功能....

快速實(shí)現(xiàn)基于FPGA的脈動(dòng)FIR濾波器,VHDL,脈動(dòng)陣列,PE處理單元,F(xiàn)IR濾波器

引言 目前,用FPGA(現(xiàn)場(chǎng)可編程門陣列)實(shí)現(xiàn)FIR(有限沖擊響應(yīng)) 濾波器 的方法大多利用FPGA....

FPGA會(huì)取代DSP嗎?FPGA與DSP區(qū)別介紹

DSP這幾年有點(diǎn)背,逐漸遠(yuǎn)離主流 話題 ,所以有人就有了這樣的問題:DSP會(huì)被FPGA取代嗎? 網(wǎng)友....

FPGA vs ASIC

FPGA vs ASIC 相同點(diǎn) 都設(shè)計(jì)使用硬件描述語言(HDL),如VHDL或Verilog。但A....