基于多相濾波的數字接收機的FPGA實現

2012年05月23日 10:43 來源:互聯網 作者:秩名 我要評論(0)

0 引言

信道化接收機是在并行多通道接收機基礎上提出的全概率頻分信道化接收機,它克服了多部接收機并行工作、多通道 下變頻等方案具有的設備復雜,各通道性能不一致和可靠性差的缺點。數字信道化接收機具備大的瞬時帶寬、較高的靈 敏度、大的動態范圍,能夠檢測和處理同時到達的信號、準確的參數測量能力和一定的信號識別能力。直接信道化接收 機的運算量大且輸出速率與采樣速率相同,實現困難,后續處理的壓力很大,高速ADO與慢速信號處理器(FPGA,DSP) 是一個“瓶頸”;基于多相濾波的信道化接收機抽取在濾波之前,運算量小,且輸出速率低,便于FPGA實現,這使得在 一片FPGA中實現數字信道化成為可能。本文利用信道頻率重疊的方法連續覆蓋整個瞬時帶寬,然后利用Rife算法測頻, 根據信道重疊的特點,消除虛假信號。系統帶寬為875 MHz(62.5~937.5 MHz),可以處理兩個同時到達的信號,并實 時給出PDW。

1 寬帶數字接收機的結構

1.1 數字信道化原理

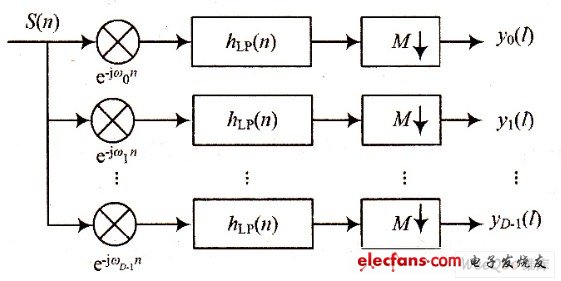

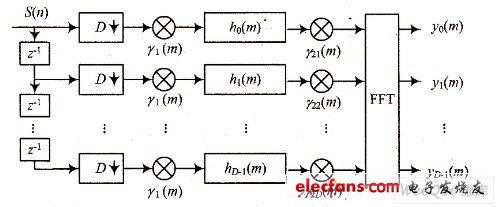

信道劃分的基本思想是把信號按頻率均勻地分成D個子頻段(即信道),每個信道的中心頻率為媽,然后分別移到零中頻,再通過低通濾波器濾出。由于子信道的帶寬遠小于系統瞬時帶寬,因此可以采用抽取的方法來降低信號的輸出速率,降低后續處理的壓力。圖1中,![]() 為低通濾波器;M↓表示對經過低通濾波器的信號M倍抽取。對于實信號而言,在偵察接收機中,各信道輸出經過M=D倍抽取后,會產生頻譜混疊,如圖2所示。各個信道的中心頻率為

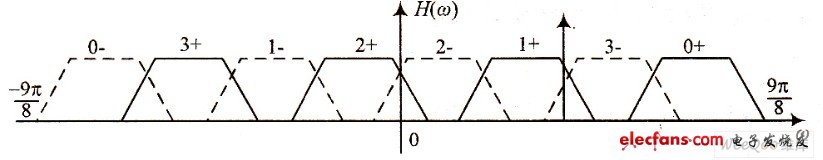

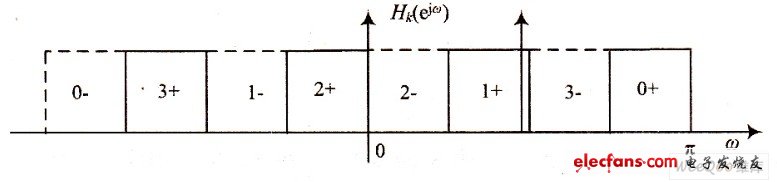

為低通濾波器;M↓表示對經過低通濾波器的信號M倍抽取。對于實信號而言,在偵察接收機中,各信道輸出經過M=D倍抽取后,會產生頻譜混疊,如圖2所示。各個信道的中心頻率為![]() ,覆蓋整個頻域范圍。但 是這種接收機存在信道的虛假輸出。由圖2中可以看出,當輸人信號位于某一信道時,靠近這一信道的相鄰信道會產生虛 假輸出。圖2中實線表示實信道,虛線表示鏡像信道。在信道化接收機的輸出端接瞬時測頻模塊,可以消除虛假信號,同時還能提高頻率精度。推導計算出混疊部分頻率的點數,在固定的某一信道,將重疊部分的點只取一次,刪除多余的點數,即消除虛假信號,得到如圖3所示的等效濾波器組。

,覆蓋整個頻域范圍。但 是這種接收機存在信道的虛假輸出。由圖2中可以看出,當輸人信號位于某一信道時,靠近這一信道的相鄰信道會產生虛 假輸出。圖2中實線表示實信道,虛線表示鏡像信道。在信道化接收機的輸出端接瞬時測頻模塊,可以消除虛假信號,同時還能提高頻率精度。推導計算出混疊部分頻率的點數,在固定的某一信道,將重疊部分的點只取一次,刪除多余的點數,即消除虛假信號,得到如圖3所示的等效濾波器組。

圖1 數字信道化原理框圖

圖2 覆蓋整個頻譜的信道分配圖

圖3 處理后的等效濾波器組

1.2 實信號無言區信道化接收機數學模型

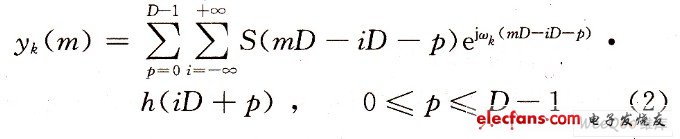

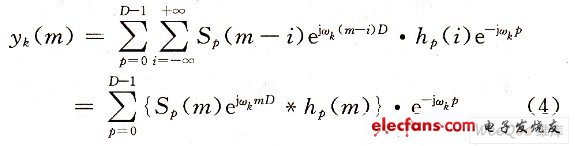

由圖1可得第乃路信號的輸出為:

令j=iD+p代入上式,得:

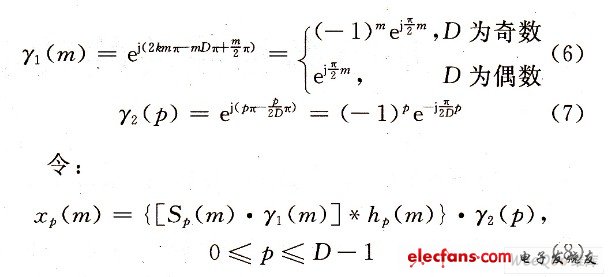

定義

![]()

則有

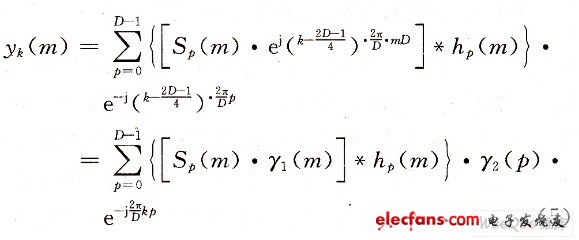

將式(1)代入式(4)得:

式(5)中

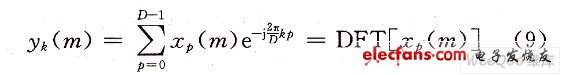

則式(5)為:

這樣得到實信號數字信道化的多相濾波實現模型,如圖4所示。

圖4 實信號頻率信道化的多相濾波實現

上周熱點文章排行榜

上周資料下載排行榜

論壇熱帖

熱門博文

創新實用技術專題

熱評

- LM3S9B96開發板手冊及原理圖

- STM32F103ZET6紅牛電路圖

- 高通發布全新設計DragonBoard板

- NI推出Single-Board RIO嵌入式介面

- protel99se正式漢化版免費下載

- hi3515海思原版原理圖

- matlab 7.0軟件下載(免費破解版)

- TX-1C型單片機開發板原理圖

- 三菱A500變頻器原理圖

- 三相IGBT全橋隔離驅動電源設計

博文

- 問什么郵箱激活不了

- 八成大學生認同先就業后擇業

- 我的心路

- 你是否曾這樣傷害過一個人?

- 為什么郵箱激活不了

- 2012.5.12 第一個DS18B20程序

- 到底有多少人在校園里浪費青春

- 藍牙技術越來越雞肋

- 【博客分享季】 我的單片機入門

- 到底有多少人在校園里浪費青春

用戶評論

查看全部 條評論

查看全部 條評論>>