基于多相濾波的數字接收機的FPGA實現(2)

2012年05月23日 10:43 來源:互聯網 作者:秩名 我要評論(0)

1.3 算法仿真

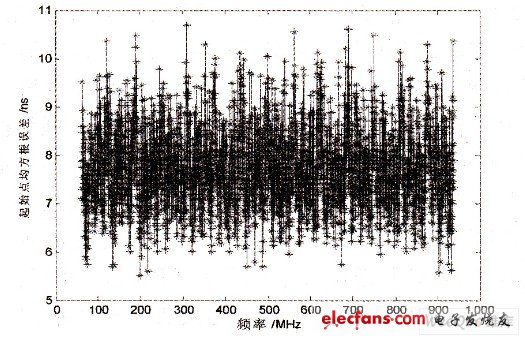

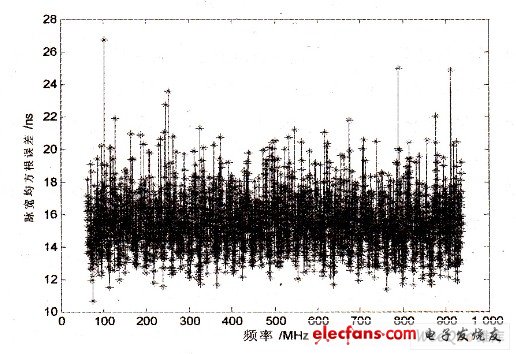

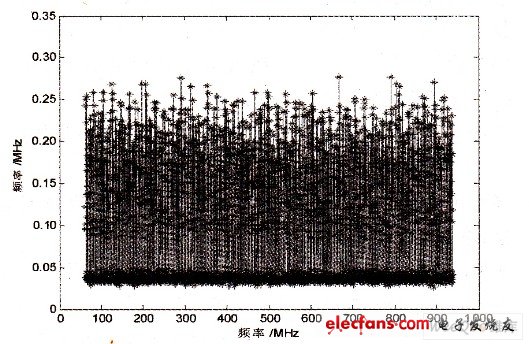

仿真時,設信號的采樣頻率為2GHz,信道帶寬為62.5 MHz,共16個信道,輸人信噪比為0 dB。輸入信號樣本為1920點(每個信道120點),信號的起始點為112 ns,脈沖寬度為600 ns。在62.5~937.5MHz 間對起始點、脈寬和頻率進行測量,頻率步長為250 kHz,參數的均方根誤差如圖5~圖7所示。

圖5 起始點均方根誤差圖

2寬帶數字接收機的FPGA硬件實現

2.1 系統模塊實現

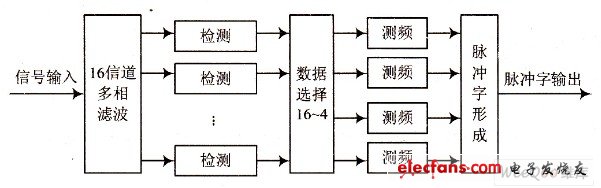

設計在Xilinx公司的XC4VSX55單片FPGA上實現,包括串并轉換模塊、多相濾波模塊、信號檢測模塊、數據選擇模塊、瞬時測頻模塊以及PDW形成模塊,如圖8所示。

圖6 脈沖寬度均方根誤差圖

圖7 頻率均方根誤差圖

圖8 FPGA系統整體結構圖

上周熱點文章排行榜

上周資料下載排行榜

論壇熱帖

熱門博文

創新實用技術專題

熱評

- LM3S9B96開發板手冊及原理圖

- STM32F103ZET6紅牛電路圖

- 高通發布全新設計DragonBoard板

- NI推出Single-Board RIO嵌入式介面

- protel99se正式漢化版免費下載

- hi3515海思原版原理圖

- matlab 7.0軟件下載(免費破解版)

- TX-1C型單片機開發板原理圖

- 三菱A500變頻器原理圖

- 三相IGBT全橋隔離驅動電源設計

博文

- 問什么郵箱激活不了

- 八成大學生認同先就業后擇業

- 我的心路

- 你是否曾這樣傷害過一個人?

- 為什么郵箱激活不了

- 2012.5.12 第一個DS18B20程序

- 到底有多少人在校園里浪費青春

- 藍牙技術越來越雞肋

- 【博客分享季】 我的單片機入門

- 到底有多少人在校園里浪費青春

用戶評論

查看全部 條評論

查看全部 條評論>>