一種基于FPGA的UART 電路實(shí)現(xiàn)(2)

2012年05月23日 10:13 來源:互聯(lián)網(wǎng) 作者:秩名 我要評(píng)論(0)

4 接收模塊

根據(jù)UART 的協(xié)議描述,可以畫出如圖3 所示的接收邏輯流程圖。接收邏輯首先通過檢測(cè)輸入數(shù)據(jù)的下降沿來檢查起始位,然后產(chǎn)生接收時(shí)鐘,利用接收時(shí)鐘來采樣串行輸入數(shù)據(jù),在緩沖器中作移位操作,同時(shí)產(chǎn)生校驗(yàn)位,在第9 位處比較校驗(yàn)位是否正確,在第10 位處比較停止位是否為高,在校驗(yàn)位錯(cuò)誤或停止位錯(cuò)誤的情況下產(chǎn)生錯(cuò)誤指示信號(hào)。接收時(shí)鐘是根據(jù)數(shù)據(jù)傳輸?shù)牟ㄌ芈十a(chǎn)生的,16 倍于波特率發(fā)生器產(chǎn)生的時(shí)鐘。

接收模塊信號(hào):

rst (輸入) : 復(fù)位信號(hào);

clk16x (輸入) : 輸入時(shí)鐘;

rdn (輸入) : 讀鎖存信號(hào);

rxd (輸入) : 串行數(shù)據(jù)輸入信號(hào);

dout [ 0: 7 ] (輸出) : 并行數(shù)據(jù)輸出總線;

fram ing_ erro r (輸出) : 幀錯(cuò)誤信號(hào);

parity_ erro r (輸出) : 校驗(yàn)錯(cuò)誤信號(hào);

data_ ready (輸出) : 數(shù)據(jù)接收完畢信號(hào)。

圖3 接收邏輯的流程

運(yùn)用Modelsim 712 對(duì)接收模塊做了時(shí)序仿真,其結(jié)果如圖4 所示。接收時(shí)鐘與發(fā)送時(shí)鐘相同,接收到一幀串行數(shù)據(jù),由接收模塊轉(zhuǎn)換為并行輸出,并且檢驗(yàn)校驗(yàn)位和停止位,產(chǎn)生fram ing_ erro r 和parity_ erro r 信號(hào)輸出。

圖4 接收模塊時(shí)序仿真波形圖

5 接口控制模塊

接口控制模塊連接控制發(fā)送、接收、波特率發(fā)生模塊,并與外部并行總線相連接,從外部(CPU 或單片機(jī)) 接收控制信號(hào)(nrst, nw rn, nbdn, nrdn) , 來控制UART 的發(fā)送、接收以及內(nèi)部時(shí)鐘的生成。在nw rn 有效并且內(nèi)部信號(hào)tbre= ′0′(發(fā)送緩沖寄存器空) 時(shí),將數(shù)據(jù)總線輸入的并行數(shù)據(jù)發(fā)送給發(fā)送模塊數(shù)據(jù)線din (7: 0) , 執(zhí)行發(fā)送數(shù)據(jù)功能。在nrdn 有效并且內(nèi)部信號(hào)data_ ready, parity_erro r, fram ing_ erro r 有效時(shí),允許從接收模塊讀入接收到的數(shù)據(jù)。波特率發(fā)生器和發(fā)送模塊的并行數(shù)據(jù)輸入端口共用一個(gè)數(shù)據(jù)總線。

6 總體電路綜合及仿真

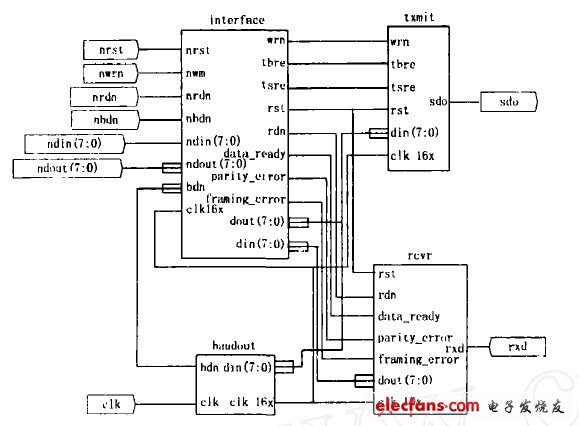

UART 總體電路如圖5 所示,分別由上述4 個(gè)模塊組成。其時(shí)序仿真如圖6 所示。

圖5 UART 總體電路圖

圖6 UART 總體時(shí)序仿真波形圖

觀察圖6, 可以看到串行輸出端口sdo 發(fā)送一幀數(shù)據(jù)為“00101011001”, 第一位為起始位,8 位數(shù)據(jù)位,校驗(yàn)位為“0”(偶校驗(yàn)) , 1 位停止位,空閑狀態(tài)位為高電平。并行輸出端口ndout 輸出為“00101010”, 輸入數(shù)據(jù)幀格式正確,校驗(yàn)位正確。

7 結(jié) 語(yǔ)

用FPGA 器件實(shí)現(xiàn)了UART 異步收發(fā)器的核心功能,可以實(shí)現(xiàn)對(duì)數(shù)據(jù)的接收和發(fā)送,并可以在接收數(shù)據(jù)時(shí)對(duì)其校驗(yàn)位、停止位進(jìn)行判斷,在發(fā)送數(shù)據(jù)時(shí)可以形成完整的一幀數(shù)據(jù)格式。其接收和發(fā)送數(shù)據(jù)的時(shí)鐘有內(nèi)部波特率發(fā)生器產(chǎn)生,根據(jù)預(yù)置的分頻系數(shù),對(duì)外部時(shí)鐘進(jìn)行分頻,產(chǎn)生需要的接收或發(fā)送時(shí)鐘。將該UART 電路作為一功能塊嵌入到一個(gè)FPGA 實(shí)現(xiàn)的數(shù)據(jù)采集與處理系統(tǒng)中,成功地實(shí)現(xiàn)了和遠(yuǎn)端的PC 機(jī)進(jìn)行異步串行通信。實(shí)驗(yàn)證明該UART 電路簡(jiǎn)單,工作穩(wěn)定、可靠,可運(yùn)用于低端的異步通信。

上周熱點(diǎn)文章排行榜

- 日本開發(fā)出用于振動(dòng)發(fā)電新合金

- 外國(guó)牛人教你一步步快速打造首臺(tái)機(jī)器人(超詳

- 全球首款惠普Z(yǔ)1電腦拆解:德州儀器、英特爾成最

- 工程師電子制作故事:無線網(wǎng)絡(luò)控制激光坦克機(jī)

- 揭秘磁懸浮燈泡無線電力傳輸(附完整電路圖)

- 華為畢業(yè)四年菜鳥身價(jià)千萬 HTC最需要害怕的新對(duì)

- 華為內(nèi)部工資和待遇詳解,50%員工空談28萬年薪?

- 易拉罐增強(qiáng)WiFi信號(hào)的方法

- 物聯(lián)網(wǎng)最新前沿技術(shù)應(yīng)用大賞(圖文)

- 最具創(chuàng)意LED發(fā)明:仿生LED隱形眼鏡 虛擬天空

上周資料下載排行榜

論壇熱帖

- 玩轉(zhuǎn)FPGA,賽靈思FPGA設(shè)計(jì)大賽活動(dòng)細(xì)則,參賽必看 wangka

- 7種你從沒想過的LED照明應(yīng)用,最后一個(gè)亮瞎了 assingle

- 2012,我們畢業(yè)啦-畢業(yè)季分享活動(dòng)正式上線 assingle

- 【博客分享季】 我的單片機(jī)入門 kisswo

- 在辦公室里自制一個(gè)植物鍵盤 assingle

- 碉堡了,這是5星級(jí)賓館的標(biāo)準(zhǔn)阿~ 東十三少

- 點(diǎn)亮iphone4 LOGO燈純手工版 技術(shù)強(qiáng)帖!!!秒殺技術(shù)宅! 心如明鏡

- 【電子拆解無極限】四核處理器露給你看 HTC One X詳細(xì)拆解 assingle

- 【我們畢業(yè)啦】二逼青歡樂多-畢業(yè)照片回顧 cch6213

- 話說今天終于收到耳機(jī)了,曬圖 小鷹fighting

熱門博文

創(chuàng)新實(shí)用技術(shù)專題

FPGA技術(shù)應(yīng)用

FPGA資料下載

- 基于FPGA的噴油脈寬處理系統(tǒng)的設(shè)計(jì)

- 基于FPGA的光纖通信系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)

- 高速成形濾波器的研究與實(shí)現(xiàn)

- 基于FPGA的高速AD轉(zhuǎn)換

- 測(cè)控系統(tǒng)中B碼同步技術(shù)的FPGA實(shí)現(xiàn)

- RFID讀卡器設(shè)計(jì)方案

- 基于高速FPGA的PCB設(shè)計(jì)技巧

- 基于FPGA的運(yùn)動(dòng)估計(jì)設(shè)計(jì)

- 基于FPGA實(shí)現(xiàn)固定倍率的圖像縮放

- 基于FPGA的數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

熱評(píng)

- LM3S9B96開發(fā)板手冊(cè)及原理圖

- STM32F103ZET6紅牛電路圖

- 高通發(fā)布全新設(shè)計(jì)DragonBoard板

- NI推出Single-Board RIO嵌入式介面

- protel99se正式漢化版免費(fèi)下載

- hi3515海思原版原理圖

- matlab 7.0軟件下載(免費(fèi)破解版)

- TX-1C型單片機(jī)開發(fā)板原理圖

- 三菱A500變頻器原理圖

- 三相IGBT全橋隔離驅(qū)動(dòng)電源設(shè)計(jì)

博文

- 問什么郵箱激活不了

- 八成大學(xué)生認(rèn)同先就業(yè)后擇業(yè)

- 我的心路

- 你是否曾這樣傷害過一個(gè)人?

- 為什么郵箱激活不了

- 2012.5.12 第一個(gè)DS18B20程序

- 到底有多少人在校園里浪費(fèi)青春

- 藍(lán)牙技術(shù)越來越雞肋

- 【博客分享季】 我的單片機(jī)入門

- 到底有多少人在校園里浪費(fèi)青春

帖子

- 【博客分享季】 我的單片機(jī)入門 kisswo

- 7種你從沒想過的LED照明應(yīng)用,最后一個(gè)亮瞎了 assingle

- 公司內(nèi)部資料共享 onejy

- 在辦公室里自制一個(gè)植物鍵盤 assingle

- 工程師應(yīng)該掌握的20個(gè)模擬電路 nf10000000

- 基于LabVIEW的數(shù)據(jù)采集與信號(hào)處理系統(tǒng)的設(shè)計(jì) 努力有理想

- labview設(shè)計(jì)憤怒的小鳥 海角一客

- 點(diǎn)亮iphone4 LOGO燈純手工版 技術(shù)強(qiáng)帖!!!秒殺技術(shù)宅! 心如明鏡

- 玩轉(zhuǎn)FPGA,賽靈思FPGA設(shè)計(jì)大賽活動(dòng)細(xì)則,參賽必看 wangka

- 發(fā)布《精通LabVIEW虛擬一起程序設(shè)計(jì)》暨-【送書活動(dòng)預(yù)告】 assingle

用戶評(píng)論

查看全部 條評(píng)論

查看全部 條評(píng)論>>